The Terasic Mercury A2700 accelerator card leverages the Altera industry’s highest performance Agilex® I-Series FPGA with 2.7M LEs to address the most compute and bandwidth-demanding applications in the data center, in the cloud, and in embedded devices.

As the first Terasic accelerator that provides 16-lane PCIe 5.0 and Compute Express Link (CXL) support, the Mercury A2700 enables 2X higher bandwidth compared with PCIe 4.0 interface for higher data throughput, as well as high-speed, low-latency, and efficient performance between CPU and FPGA.

By leveraging the CXL IP, the Mercury A2700 can seamlessly connect to high-bandwidth processors and CXL compatible memory devices via the CXL interface to achieve lower latency data processing speed, enhancing performance in compute-intensive workloads such as high-performance computing (HPC), AI, machine learning, high-frequency trading, and data analytics.

Key Benefits

- Altera® Agilex® I-Series FPGA with 2700K Logic Elements. Core Speed Grade : -2 / XCVR Speed Grade : -1 or -2

- PCI Express Gen 5.0 x16 and CXL x16 (Note*) with full-height, 3/4-length form-factor package

- Two QSFPDD connectors for 200/100/40/25/10 GbE network interface

- Two MCIO 8x connectors to support PCIe and CXL (Note*)

- Four DDR4 SO-DIMM sockets with error correction code (ECC) for both FPGA and HPS fabric

- HPS communication interface with USB to UART, MicroSD socket and Gigabit PHY, and USB OTG

Note*:

- Available only for transceiver speed -1

- CXL requires licensing that is sold separately from the card

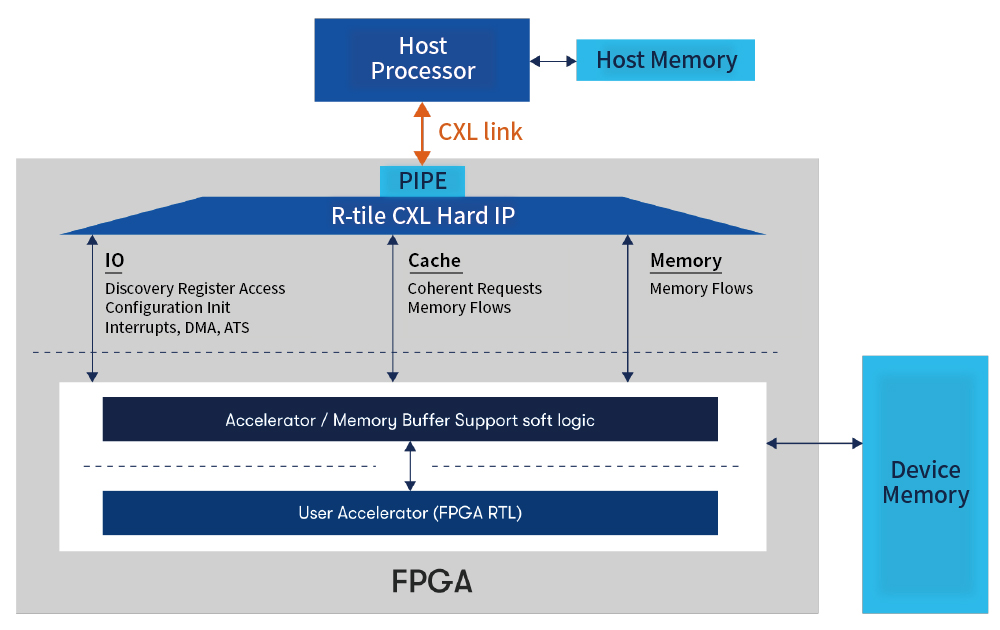

Getting Started to Develop with CXL IP

- The Intel FPGA CXL IP solution comes as a combination of hard IP and soft IP support logic. To design with Intel FPGA CXL IP, customers need to purchase a separate IP license.

- After the CXP IP license is activated, you will be able to find the CXL IP in the Intel Quartus Prime Software IP Library.

- Once the R-Tile CXL hard IP block is activated, and then the appropriate soft IP is added. The FPGA designer can interface to the support logic by adding other user logics or acceleration functions into the design.