作者 – 友晶科技资深技术经理 杨至信先生 (Altera ACAP 顾问)

在此所述的 PIP (Picture In Picture) 功能,是指能在同一屏幕上显示出两个以上影像源 (Video Source) 而言。在一般消费性产品上,例如目前 LCD TV 中,此 PIP 功能就常常被要求规划进去。然而此 PIP 得以被考虑,其主要的原因是:(一) 为现在 Video 的讯号被普遍的数字化,使得讯号的储存更加方便,此将很容易的去储存一个 Frame 的 Video 讯号。以前的模拟电视机大都无法提供此项功能。(二) 在于现代家庭中都已拥有多个影像输出装置。如除了电视机本身中的调谐器 (Tunner) 外,家中也可能有 VCD 播放机、DVD 播放机、有双调谐器的 TV、Set to Box、 DSC (有 TV out 功能的)、CCD 监视器等。

若你的电视机拥有 PIP 功能时。就可以在不影响观看者观看的情况下,另一影像讯号源,由电视机的另一个 Video IN 输入。并在按下电视摇控器的 PIP 切换扭。电视屏幕上会自动开出一个小窗口,另一影像将会出现在屏幕的小窗口上。使用者将可方便监看另一节目或监视另一影像的动态,以达到统一并方便控制的目地。

此 PIP 的功能也可应用在一般的影像处理工程或医学影像分析工程上。分析者除了能看到当下实时播放之影像外。亦可利用此子画面,去显示主画面影像处理的实时结果。如实时显示当下画面的 DCT 处理结果、颜色处理结果、FIR 处理结果等。分析者或学习者,马上就可看到此影像被处理后的结果。经一比对,分析者或学习者,不难留下一个深刻的印象。

验证功能时的挑战

PIP 功能设计的方式。也可以以算法常用的软件包,如 Matlab 来进行。其处理后的每一张图片,就先预存起来。然后,再用播放软件将每一张图整合起来播放。但是此方法会使处理时间变长,也会使图的管理变得烦琐。如原始影像截取的每张图片的管理,与处理后的每张图片的管理。之后的汇整或编排,会因大量的数据量之处理,显得费工又费时。因此,在业界已开始去用 HDL (Verilog or VHDL) 实时验证法来进行之。

我们实作结果发现,用 HDL 来编写讯号处理的 RTL CODE, 并不会比用C 语言等,编写出来的 CODE,困难度增加太多。而且目前 FPGA 商,除了提供 FPGA 组件外,也支持 RTL 语言合成 (synthesis) HDL 编码 -- 都支持 Verilog 与 VHDL 等硬件描述语言的合成,再用其适当等级的 FPGA。使用者就可实现实时处理的验证与设计 -- 将不再需要靠软件等,非实时性的模拟方式,来验证结果。如 PIP 这个主题,在大架构的规划与编码完成后。每一次因修改,而须重新合成所花费的时间,将可以短至 10 分钟以内。合成之后,就可立即下载到 FPGA 中。结果正确与否,马上就可得知。

正确的系统平台配置

FPGA 之应用,对于急于想得知结果者而言,是一个正确的选择。但要仔细考虑验证平台的架构,是用何种方式来组合的。我想,这也是每一位 FPGA 使用者,所要面对的重要课题。例如,这个 PIP 主题。是预计要达到 real time 子母画面 (PIP) 的功能。故在系统规划上,须安排两个影像输入界面、一个影像输出界面、双埠 Memory、PLL 与其它控制电路等。以此,我们下节将开始来探讨,一个理想验证平台之架构规划。

系统平台规划 – 传统方案

一般 FPGA 平台上,其 FPGA 外部至少要安排 512K Bytes 的 Memory,去做 Frame Buffer。而如此大的 Memory Buffer,一般会考虑用 SDRAM。此对于拥有 SDRAM Controller 者或是常常在使用 SDRAM 者,此 SDRAM 是很容易被控制的。但对于从算法背景出发的验证工程师,SRAM 就比较能直觉反应储存的状况, 控制起来也比较单纯。但不管以哪种方式,用1440 x 262 = 377280 bytes 的 Frame Memory (以NTSC@60Hz with 480i而言),是基本需求。故外加 Memory 在此验证平台上是必要的。而且,不管是外加 SRAM 或 SDRAM,其数据的存取也需要被安排成 dual_port RAM 的行为模式。

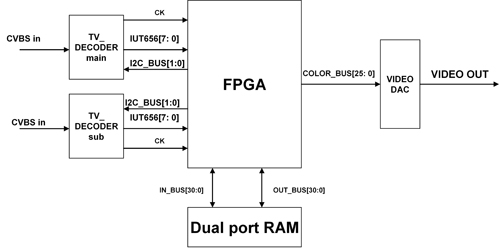

若使用者手边只有一般通用型 FPGA 验证板的话。 板子的安排可能会如下图所示 -- 在 FPGA 的周围所环绕的脚将不下120 PIN。而且当在作多种子母画面比率的切换时, Memory asscess 控制会很频繁,FPGA 与 Memory 讯号会很复杂,无谓的噪声与干扰将会混合在一起,使得板子的不稳定性与错误率将会变大。

系统平台规划 – Altera 最新数字电视平台方案

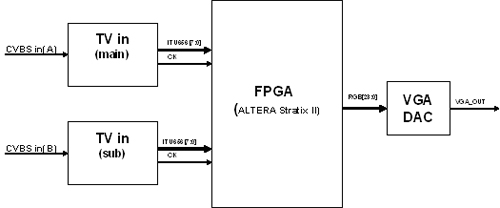

Altera 目前推出一个有如堆积木式概念之平台。利用两种低价高效能平台内的 TV decoder 与其中的数字处理电路,先作 TV in 输入电视的 CVBS 模拟讯号转数字讯号之界面电路。之后,将得到的两个数字电视讯号,传到高效能的 FPGA 中,统一控制与处理。最后传到 VGA DAC,并用一般的 VGA monitor 来观看,很快就可看到处理与验证后的结果。如此一个数字电视验证平台,其方块图组成如下图所示。此验证平台中的高效能 FPGA 将可被规划设计作,如 PIP、De_interlace、Scaler、DCT 或其它等复杂度较高的算法之 Real Time 验证。

IC/FPGA方块图规划

此就以 PIP 规划设计为例。首先,安排两个一般 TV decoder 输出的 ITU 656 YUV 4:2:2 数字讯号作输入。此只取两影像讯号中的8位数字数据流与其 CLOCK 就可以。并任选一个影像作为主画面,另一个影像讯号就作子画面。也预计先以固定整数比 4:1 的 PIP 为设计。也就是,设计后的子母大小比率,子画面是母画面的 1/4 倍。

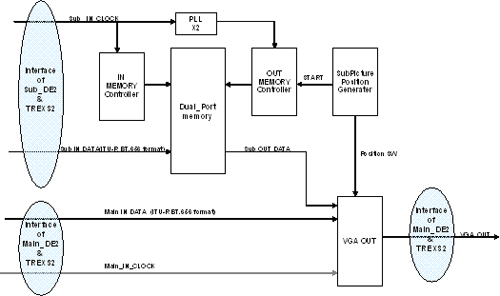

就以上考虑点出发 。规划上,首先将主画面的 CLOCK 输入到一个 x2 的 PLL 中,以得到两倍的 CLOCK 输出,作为将来子画面播放的 CLOCK 用。也为了使 “主” 与 “子” 画面的影像要不能互相干扰,考虑用可储存到一个 Frame 大小的 RAM 来储存子画面的输入数据。而此 RAM 的型式之也必须有所选择。因 RAM 中的数据会在 PIP 功能打开后,以两倍的速度被读出来。更有可能在未来 PIP 的规划上,被修改成子母画面大小比率为任意比率的。此时 RAM 的数据,会以任意倍率的速度被读取。就以此考虑RAM 的型式,是要选择输入输出的 Address BUS 与 Data BUS 是完全独立的-- dual port RAM。那么,RAM 输入输出数据存取控制才能完全独立。

此外,子画面的出现也希望可以在整个屏幕的任意位置,故再安排一个子画面的起始点坐标产生器。此产生器将决定,并控制 dual port RAM 的输出 Address BUS Counter 何时开始计数与何时数据开始被读取。同时,也要去告知,主画面的影像数据流何时要让开,去换成子画面的影像数据流输出。

最后,再安排几个 KEY,去作 PIP 的 ON/OFF 与子画面的位置控制切换开关。整个架构就可如下面方块图所示,此架构就可移入此高效能的 FPGA 中,一次完成设计与验证。

实作结果效能分析

此次我们以 Altera 数字电视平台来实作 PIP,以 Altera DE2 (多媒体开发平台) 及 TREXS2 (StratixII为FPGA) 两者来作整合。因 DE2 拥有多个多媒体界面,TREXS2 有高速超大的 Gate count 与超大的 Memory 资源。在一周内完成了这个专题,共享了两片 DE2 与一片 TREXS2 180 (StratixII 180F1020)。

完全秉除了,早期对 FPGA 操作不易(可能要焊BGA 的IC) 与资源不足而须大量依赖其它连结板的痛苦经验。故在坐拥 90nm 等级的 FPGA 下,使用者应可大胆去创造自已的IP。不再需要怕为了影响讯号的质量,而太过仔细考虑架构的安排,让宝贵的创意无法被尽情的发挥。

结语

在先进制程的不断推出,IP的大整合与消费者的多样化的需求下,使得 IC 设计者对 real time 与精准验证工具之须求更加殷切。但当在无足够经验的 FPGA 发展板之规划工程师时,慎选 FPGA 发展平台与转板将是 IC 设计者的重要任务。 若选错了或是因转板的关系,使得 FPGA 的性能大打折扣,进一步使得 IC 验证出现了盲点。

IC 设计者的 IP 必定是在 PC 上,花了许多时间模拟完,也确实无误了。才会移到 FPGA 平台作 real time 验证。但却照成更多的争议,此乃使得一些 IC 设计者不相信 FPGA 验证结果的原因。

因此对于 FPGA 高性能的重现,是 FPGA 发展板之规划工程师与从事开发 FPGA 发展板的厂商,必须努力以对的。

作者照片