(Terasic News Report)

Science and technology bring convenience to today's life. What we have today is the outcome of the efforts and innovation of scientists and engineers. For decades, scientists and engineers have been working to develop mechanical appliances and robots to help save lives and to save time and money in businesses. Many robots and current technologies are helpful but we still need improvements in some areas, such as how to make the robot more human, more economical to use, and smoother in its motions so it saves time and money.

|

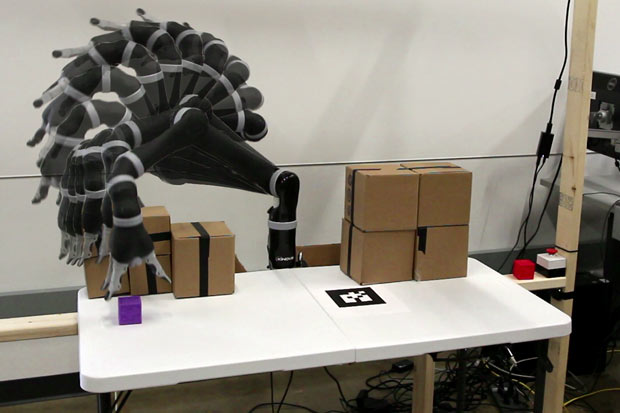

Jaco robot arm doing motion planning with custom FPGA processor |

The IEEE Spectrum has an article on "Motion-planning Chip Speeds Robots" indicating that Duke University's research team recently overcame the problems of Robot's time consuming arm and gripper pausing problem due to a motion planning algorithm via the use of Terasic's DE5-Net

FPGA. The researchers found a way to speed up motion planning while only using one-twentieth of the power, increasing the efficiency of the robot's range of motion. The primary step was to put the robot in operation without the possibility of collision, and using custom processors to deal with motion trajectory. This helped to prevent the mechanical standstill.

The researchers first develop a probability roadmap. This roadmap which is a graph contains a number of points in the obstacle-free space. The robot has been set up so that part-time movement will not result in a collision of the obstacle, and finally figure out the optimum path in the PRM from the start point to the end point. During the movement of the robot arm space may also be a chance for a collision, so the robot's arm through the space for the movement (swept volume) must be considered in the calculation. These steps and calculations are extremely challenging. One study showed that collision detection consumed 99 percent of a motion planner's computing time.

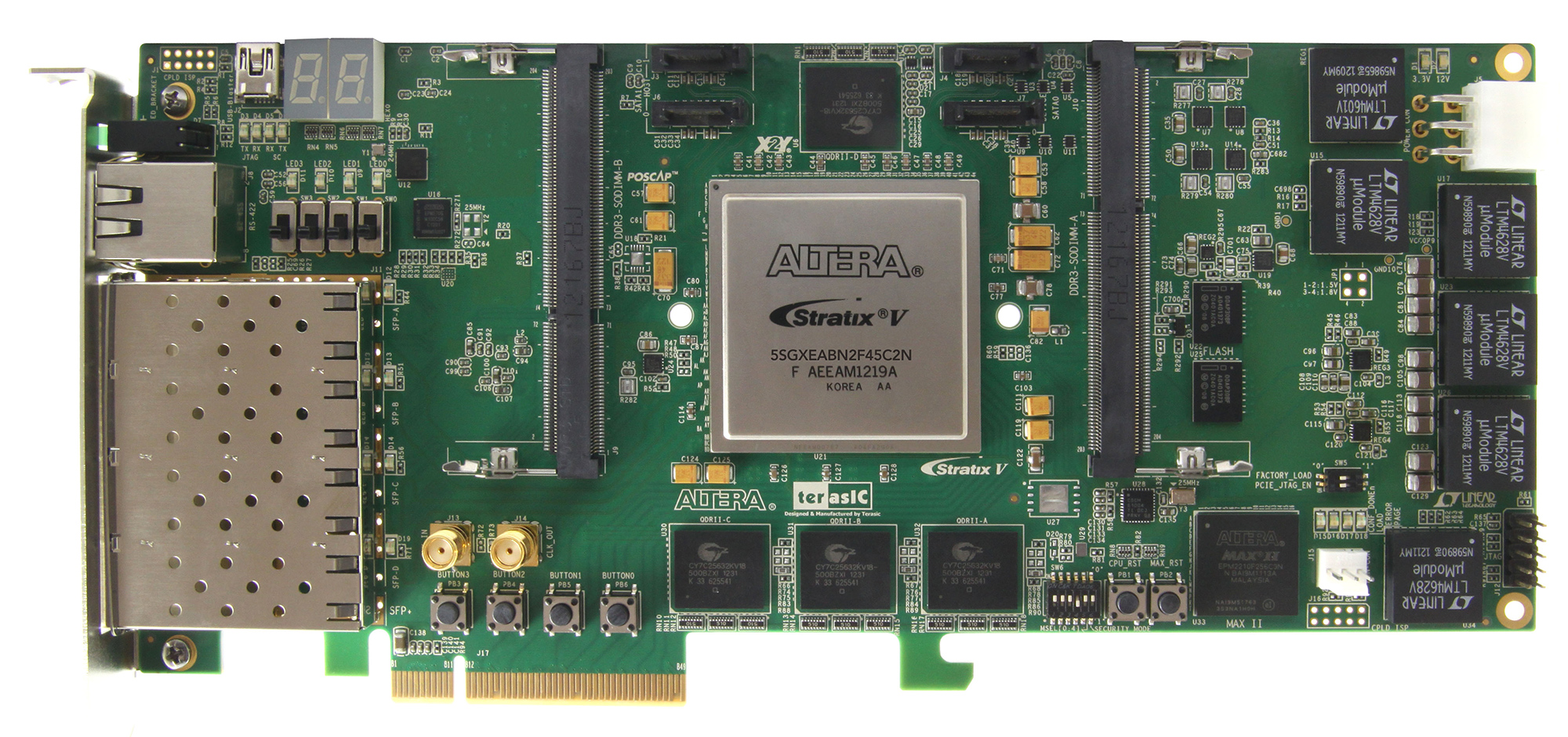

DE5-Net FPGA Development Kit

In addition to Terasic DE-5-Net's

robotics acceleration, the Terasic DE5-Net

is ideal for applications such as no-delay transactions, cloud computing, high-end computing, data, networking and signal processing.. The DE5-Net

uses Intel Stratix V GX FPGAs, supports PCI Express 3.0, and four external 10G SFP +. The DE5-Net

accelerates network applications without relying on an external PHY. (For more information on DE5-Net, please click this link

)

DE5a-Net Arria 10 FPGA Development Kit

For faster network communications applications, Terasic offers the PCI Express development board DE5a-NET with the latest Arria 10 GX FPGAs; This provides four 40G QSFP ports. (For more information on DE5a-Net, please click this link

)

Terasic is the best partner to help you design your work or if you need help choosing the best board for your project so that your design can achieve the best result in the shortest possible time or have any questions about our products, you can contact us at Sales@terasic.com

.

(Source: IEEE

)

IEEE Report: Motion-Planning Chip Speeds Robots