[ 2012/6/22, Terasic Technologies ]

The University of Massachusetts at Amherst has announced that the NetFPGA program has been successfully ported to the DE4 Stratix IV GX FPGA Development Kit ! A powerful open source-networking platform for prototyping high-speed, hardware-accelerated networking systems, NetFPGA is primarily aimed for students and researchers for learning about the development of gigabit Ethernet interfaces, networking protocols, and more.

The heart of the platform is the FPGA development board that provides the hardware peripherals and connectivity. Utilizing an FPGA provides a low-cost, highly agile method of experimenting with different kinds of network solutions.

Until recently, the only development board available was a Xilinx Virtex II board, but that has changed recently. With the support of Altera, the University of Massachusetts Amherst’s Reconfigurable Computing Group has successfully ported it over to the Altera DE4 FPGA Development and Education Kit .

One advantage of using the DE4 is that researchers who are used to Altera design tools now have an Altera alternative to choose. The second advantage lies in the feature set of the DE4 .

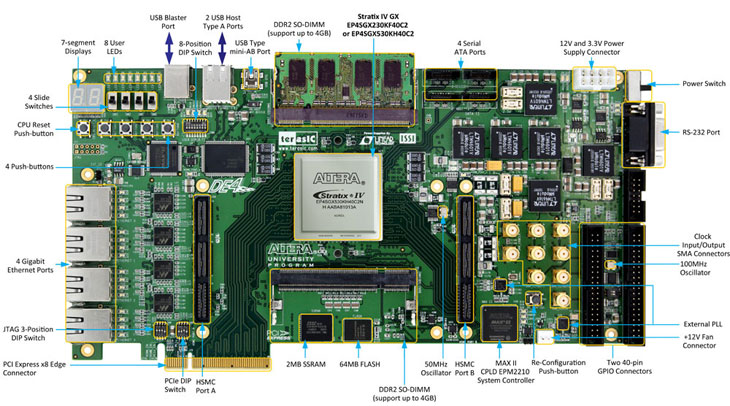

Figure 1. DE4 FPGA Development Kit Feature Set

According to the University of Massachusetts page, “With the growing requirements of recent research projects, the small size of NetFPGA’s on-board Virtex II Pro 50 (about 53,000 LUTs) limits its usefulness for many applications. Moreover, the 33 MHz NetFPGA PCI interface is a bottleneck for host-card data transfer.

On the DE4 board , the EP4SGX230 FPGA (about 228,000 LUTs) has more than 5 times logic elements. The board also has a larger BRAM, supports up to 8GB external DRAM, and supports PCI Express.”

Also featured is a comparison chart between the two boards:

| NetFPGA | DE4 | |

|---|---|---|

| FPGA | Virtex II | Stratix IV GX |

| Logic Cells | 53,136 | 228,000 |

| Block RAM | 4,176Kbit | 17,133Kbit |

| GIGE | 1Gx4 | 1Gx4 |

| SRAM | 4.5MB | 2MB |

| DDR RAM | 64MB On Board | Up to 8GB External |

| PCI Express | No | Yes (Up to 2 Hard IP cores) |

| JTAG Support | Yes | Yes |

| PHY Interface | Broadcom | Marvell |

Be sure to check out more at the University Page for more information on how to obtain the software and FPGA configuration files.

It’s an exciting time for network experimentation, with more applications being uploaded to the wiki page everyday. Be sure to participate in the movement by uploading your own creations and sharing knowledge with the open source world!