|

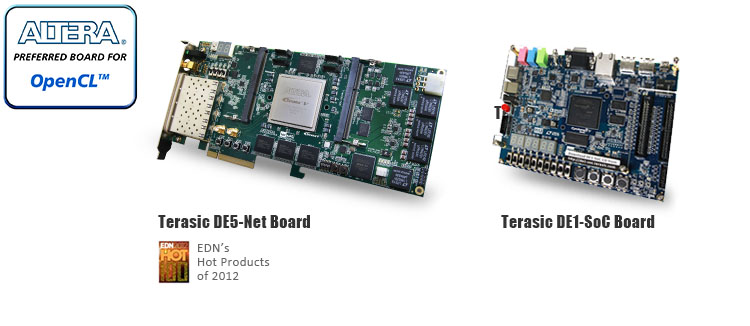

Terasic DE5-Net board and DE1-SoC board now officially support the OpenCL Computing Language (OpenCLTM ) programming model. Experience the incredible performance boost using our most powerful solution! |

Terasic OpenCL Bundle

Terasic OpenCL Bundle is special offer for Terasic DE5-Net Board ONLY !

DE5-Net Board:

- Altera Stratix® V GX FPGA (5SGXEA7N2F45C2)

- Up to 8GB DDR3 800 MHz SO-DIMM SDRAM

- 32MB SRAM (ISSI QUADP for DE5-Net 450, GSI SigmaQuad-II+ for DE5-Net 550, Cypress QDRII+ for DE5-Net 500)

OpenCL License Bundle includes:

- A license for Altera's SDK for OpenCL

- A one-year evaluation license for Quartus® II Development Kit Edition software

As more and more real-life applications in various fields, such as pharmaceutical, bioinformatics, HFT in financial market, and others, require OpenCL implementations, we are confident that DE5-Net FPGA Development Kit is an ideal OpenCL platform that gives satisfactory results in both performance and cost.

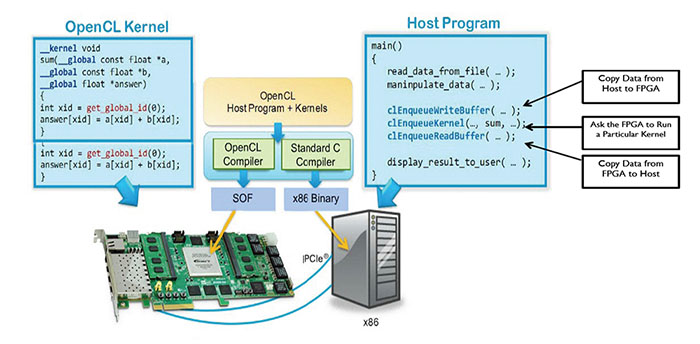

OpenCL Platform Example

HPC (High-Performance Computing) platform

- Features high bandwidth on-board memory and powerful computing resource of Stratix V GX FPGA

- High speed PCIe interface to the host system (up to 8GB/s per lane) enabling the FPGA to act as a Co-Processor working together with other processing units within the system.

- OpenCL programmers can easily target the FPGA fabric without in-depth knowledge of a FPGA chip

>> Download HPC BSP for DE5-Net

>> Download HPC BSP for DE1-SoC

What is OpenCL?

Since the advent of modern re-programmable ICs, FPGAs have long been touted as the next era of supercomputing. The dream, however, is still currently hindered due to present hardware description languages such as Verilog and VHDL which are too low-level for the majority of current software engineers to adopt. That’s where OpenCL steps in.

Currently managed by the Khronos Group, OpenCL is a new standard in programming that takes the high-level convenience of the C programming language and applies it to the parallel nature of FPGAs. If adoption is successful, the implications could be phenomenal. According to Altera’s whitepaper, “FPGAs may offer significantly higher performance and at much lower power than is available today from hardware architectures such as CPUs, graphics processing units (GPUs), and digital signal processing (DSP) units.”

High-end DE5-Net FPGA Development Kit Paired with Host Computer

Why use OpenCL for Altera FPGAs?

【Learn More】

- More information for DE5-Net FPGA Development Board: de5-net.terasic.com

- More information for DE1-SoC FPGA Development Board: de1-soc.terasic.com

- More OpenCL: http://www.khronos.org/opencl/

- More Altera’s Preferred Board Partner Program for OpenCL:

http://www.altera.com/products/software/partners/opencl/opencl-board-partner-index.html

OpenCL Board

DE1-SoC Board:

- Altera Cyclone V SoC 5CSEMA5F31C6 Device

- 1GB (2x256Mx16) DDR3 SDRAM on HPS

- 64MB (32Mx16) SDRAM on FPGAConverting OpenCL C code for FPGA implementation in a single step

- Consumes less power by only generating the necessary logic with Altera SDK tool