SIF User manual

From Terasic Wiki

(→Overview) |

(→TMD Expansion Header) |

||

| (21 intermediate revisions not shown) | |||

| Line 1: | Line 1: | ||

=Overview= | =Overview= | ||

The '''SIF-TMD''' card can provide serail communication function (USB to UART) to the motherboard, users can connect this daughter card to FPGA motherboard which equipped Terasic TMD connector or GPIO connector (use jump wire) to get the UART protocal feature.User only need to connect the Host to the SIF-TMD card through the USB cable to establish the serail data transmision between the FPGA and the Host. In addition, the SIF-TMD also provides I2C interface EEPROM and SPI interface FLASH, allowing users to use FPGA to access these memories to realize the features of data access. | The '''SIF-TMD''' card can provide serail communication function (USB to UART) to the motherboard, users can connect this daughter card to FPGA motherboard which equipped Terasic TMD connector or GPIO connector (use jump wire) to get the UART protocal feature.User only need to connect the Host to the SIF-TMD card through the USB cable to establish the serail data transmision between the FPGA and the Host. In addition, the SIF-TMD also provides I2C interface EEPROM and SPI interface FLASH, allowing users to use FPGA to access these memories to realize the features of data access. | ||

| - | + | ||

| + | |||

[[File:SIF-TMD 45 02.jpg|400px]] | [[File:SIF-TMD 45 02.jpg|400px]] | ||

| + | |||

| + | '''Board Featue :''' | ||

| + | |||

| + | * USB to UART function | ||

| + | **Emulate standard serial interface, used to upgrade the former peripheral device, or add excess serial interface through USB | ||

| + | **Supports baud rate varies from 50bps to 2Mbps. | ||

| + | * One I2C interface 32Kb EEPROM | ||

| + | * One SPI Interface 8Mb Flash | ||

| + | |||

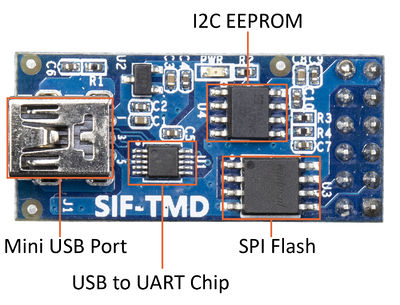

| + | The following two pictures show the board components of SIF-TMD: | ||

| + | |||

| + | *Top View | ||

| + | |||

| + | [[File:SIF-TMD Top Layout.jpg|400px]] | ||

| + | |||

| + | *Botton View | ||

| + | |||

| + | [[File:SIF-TMD Bot Layout.jpg|400px]] | ||

| + | |||

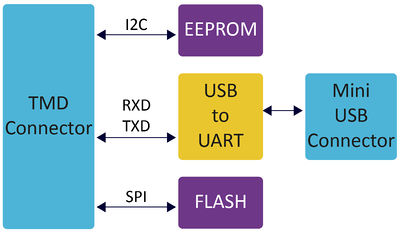

| + | The following picture shows the block diagram of the SIF-TMD card. | ||

| + | |||

| + | [[File:SIF-blockdiagram 01.jpg|400px]] | ||

| + | |||

| + | =Components= | ||

| + | This chapter will introduce the hardware components of the SIF-TMD card. | ||

| + | ==USB to UART Interface== | ||

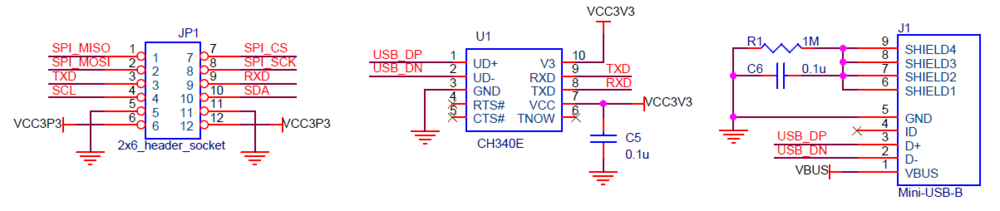

| + | The UART serial interface is designed to perform communication between the board and the PC. he physical interface is done using UART-USB on-board bridge from a CH340E chip and connects to the host using a Mini-USB connector. The CH340E on the SIF-TMD card wouldn’t support HW flow control signals and it provides TXD and RXD signals to the TMD connector on the SIF-TMD card. Also the chip supports communication baud rate varies from 50bps to 2Mbps. For detailed information and host driver for the CH340E chip, please refer to the datasheet, which is available on the [http://www.wch-ic.com/downloads/CH340DS1_PDF.html manufacturer’s website]. | ||

| + | |||

| + | [[File:Sif tmd uart circuit.png|1000px]] | ||

| + | |||

| + | == TMD Expansion Header == | ||

| + | |||

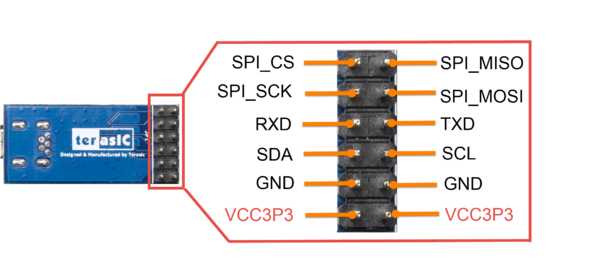

| + | The board has one 2x6 TMD (Terasic Mini Digital) expansion header. This header can be connected to the FPGA host board that featured the expansion header or use jump wire to connect to the GPIO header of the host board. | ||

| + | The TMD header has 8 digital GPIO user pins connected to the FPGA host board, two 3.3V power pins and two ground pins (provided by FPGA host board). | ||

| + | The 8 digital GPIO of the TMD header are connected to the USB to UART, EEPROM and Flash devices on the SIF-TMD card, so the host board can use these interface for expansion. The follwoing picture shows the pin out of the TMD header. | ||

| + | |||

| + | [[File:Sif tmd pinout.png|600px]] | ||

Latest revision as of 16:52, 4 August 2021

Contents |

Overview

The SIF-TMD card can provide serail communication function (USB to UART) to the motherboard, users can connect this daughter card to FPGA motherboard which equipped Terasic TMD connector or GPIO connector (use jump wire) to get the UART protocal feature.User only need to connect the Host to the SIF-TMD card through the USB cable to establish the serail data transmision between the FPGA and the Host. In addition, the SIF-TMD also provides I2C interface EEPROM and SPI interface FLASH, allowing users to use FPGA to access these memories to realize the features of data access.

Board Featue :

- USB to UART function

- Emulate standard serial interface, used to upgrade the former peripheral device, or add excess serial interface through USB

- Supports baud rate varies from 50bps to 2Mbps.

- One I2C interface 32Kb EEPROM

- One SPI Interface 8Mb Flash

The following two pictures show the board components of SIF-TMD:

- Top View

- Botton View

The following picture shows the block diagram of the SIF-TMD card.

Components

This chapter will introduce the hardware components of the SIF-TMD card.

USB to UART Interface

The UART serial interface is designed to perform communication between the board and the PC. he physical interface is done using UART-USB on-board bridge from a CH340E chip and connects to the host using a Mini-USB connector. The CH340E on the SIF-TMD card wouldn’t support HW flow control signals and it provides TXD and RXD signals to the TMD connector on the SIF-TMD card. Also the chip supports communication baud rate varies from 50bps to 2Mbps. For detailed information and host driver for the CH340E chip, please refer to the datasheet, which is available on the manufacturer’s website.

TMD Expansion Header

The board has one 2x6 TMD (Terasic Mini Digital) expansion header. This header can be connected to the FPGA host board that featured the expansion header or use jump wire to connect to the GPIO header of the host board. The TMD header has 8 digital GPIO user pins connected to the FPGA host board, two 3.3V power pins and two ground pins (provided by FPGA host board). The 8 digital GPIO of the TMD header are connected to the USB to UART, EEPROM and Flash devices on the SIF-TMD card, so the host board can use these interface for expansion. The follwoing picture shows the pin out of the TMD header.