Terasic USB Blaster revB Manual

From Terasic Wiki

(→Using the Intel FPGA Download Cable) |

(→Using the Intel FPGA Download Cable) |

||

| Line 171: | Line 171: | ||

[http://www.terasic.com.tw/wiki/Altera_USB_Blaster_Driver_Installation_Instructions Altera_USB_Blaster_Driver_Installation_Instructions] | [http://www.terasic.com.tw/wiki/Altera_USB_Blaster_Driver_Installation_Instructions Altera_USB_Blaster_Driver_Installation_Instructions] | ||

| - | * | + | *Install the drivier for Linux |

[https://rocketboards.org/foswiki/Documentation/UsingUSBBlasterUnderLinux Using USB Blaster Under Linux] | [https://rocketboards.org/foswiki/Documentation/UsingUSBBlasterUnderLinux Using USB Blaster Under Linux] | ||

Revision as of 11:06, 18 December 2019

Contents |

Introduction

The main function of the Terasic USB Blaster Download Cable (UBT) is to allow users to download configuration data to the system during prototype development, or to program data into the system during production. The UBT connects the Host and the FPGA on the user's board through the USB Port and 10-Pin cable. At the same time, it can support several target board voltage standards, allowing UBT to be widely used in various FPGA boards.

Supported Devices and Host System

The Intel FPGA , Serial configuration device and host systems that UBT supported are list in Table 1-1, Table 1-2 and Table 1-3

| FPGA Serie | Deivce |

|---|---|

| Stratix Series | Stratix 10, Stratix V, Stratix IV, Stratix III, Stratix II GX and Stratix GX |

| Arria Series | Arria 10, Arria V, Arria II, Arria GX |

| Cyclone Series | Cyclone 10,Cyclone V, Cyclone IV, Cyclone III, Cyclone II, Cyclone |

| MAX series | MAX10,MAX V, MAXII , MAX3000, MAX7000 and MAX9000 |

| Other | FLEX10K, ACEX1K, APEX 20K |

| FPGA Serie |

|---|

| EPCS devices |

| EPCQ devices |

| EPCQ-L devices |

| Host System |

|---|

| Window |

| Linux |

Operating Conditions

UBT can support several voltage standard of the target board. Table 1-4 shows the supported voltage. Users need to pay attention to whether the JTAG voltage standard of the Targer board is within the range of Table 1-4.

| Support Target board supply voltage |

|---|

| 1.2V (*1) |

| 1.5V (*1) |

| 1.8V (*1) |

| 2.5V |

| 3.3V |

(*1) Only Rev .B can supoort .

Pin define

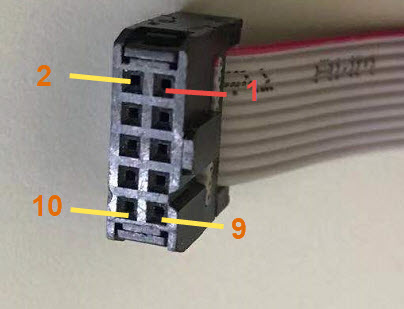

The following picture and table list the pins of the Terasic Download Cable female plug and describes their functions in the JTAG and passive serial modes.

| Pin Number | Pin Define | JTAG Mode Descriptions | PS Mode Descriptions |

|---|---|---|---|

| 1 | TRGTCK | Clock signal | Clock signal |

| 2 | GND | Signal ground | Signal ground |

| 3 | TRGTDO | Data from | Configuration done |

| 4 | TRGVCC | Target power supplied by the device board | Target power supplied by the device board |

| 5 | TRGTMS | JTAG state machine control. | Configuration control. |

| 6 | TRGNCE | - | - |

| 7 | TRGNST | - | Active serial data out |

| 8 | TRGNCSO | - | Serial configuration device chip select |

| 9 | TRGASDO | Data to device. | Active serial data in |

| 10 | GND | Signal ground. | Signal ground |

Using the Intel FPGA Download Cable

To start using the Intel FPGA Download Cable, user need to install the drivers on your system and set up the hardware in the Intel Quartus® Prime software.

To program or configure the device, connect the host system to the device board using the Terasic Download Cable and initiate the programming or configuration using the Intel Quartus Prime Programmer. You can also use the cable with the Intel Quartus Prime Signal Tap Logic Analyzer for logic analysis.

- Install the Driver for windows

Altera_USB_Blaster_Driver_Installation_Instructions

- Install the drivier for Linux