DE10-Advanced User Manual

From Terasic Wiki

Contents |

Chapter 1 DE10-Advanced Development Kit

Terasic A10SOC is a kind of the best SoC FPGA development platform with various advanced interfaces. It built around the Intel Arria 10 SoC FPGA, which combines the dual-core ARM Cortex A9 CPU and provides 660K LEs. A10SOC has many peripherals, it can transfer data to PC with a high speed through PCIEx4 GEN3 and Type-C USB connector. The four SFP interfaces and Gigabit Ethernet port can be used in network application. HDMI 2.0 output and the two DDR4 SODIMMs allow users to deal with high bandwidth of image. A10SOC provides a FMC connector, it can extend more development space. Generally speaking, A10SoC has powerful computing and interface processing capacity, it must be the best choice for Network Communication, High Performance Computing, Image Processing and other applications.

Package Contents

The DE10-Advanced package includes:

- The DE10-Advanced board

- Quick Start Guide

- TBD

DE10-Advanced System CD

The DE10-Advanced System CD contains all the documents and supporting materials associated with DE10-Advanced, including the user manual, system builder, reference designs, and device datasheets. Users can download this system CD from the link: http://DE10-Advanced.terasic.com/cd.

Getting Help

Here are the addresses where you can get help if you encounter any problems:

Terasic Technologies

9F., No.176, Sec.2, Gongdao 5th Rd, East Dist, Hsinchu City, 30070. Taiwan

Email: support@terasic.com

Tel.: +886-3-575-0880

Website: DE10-Advanced.terasic.com

Chapter 2 Introduction of the DE10-Advanced Board

This chapter provides an introduction to the features and design characteristics of the board.

Layout and Components

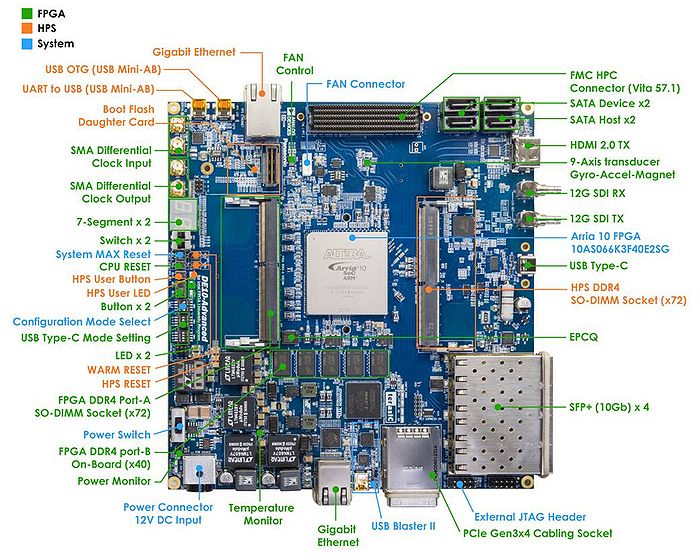

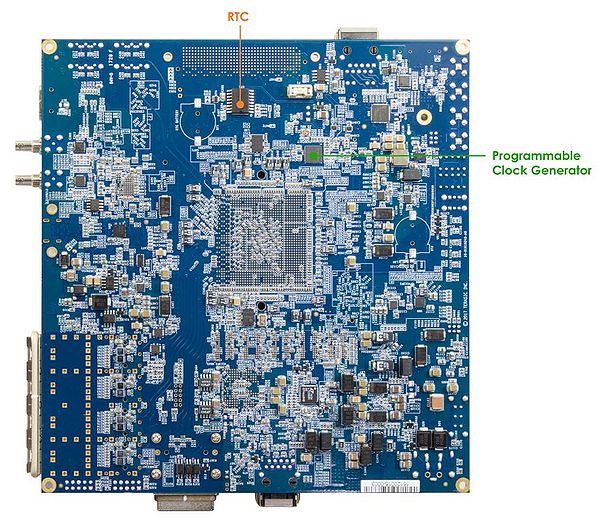

Figure 2-1 and Figure 2-2 shows a photograph of the board. It depicts the layout of the board and indicates the location of the connectors and key components.

- Figure 2-1 DE10-Advanced development board (top view)

- Figure 2-2 DE10-Advanced development board (bottom view)

The DE10-Advanced board has many features that allow users to implement a wide range of designed circuits, from simple circuits to various multimedia projects. The following hardware is provided on the board:

- FPGA

- USB Type-C Interface: Power Delivery, DisplayPort TX/RX with 4 lanes, USB 3.0/2.0

- HDMI TX 2.0 for 4K2K@60. Use FPGA Transceivers

- PCIe Cabling Socket at Gen3 x4

- SFP+ Socket x4,40Gbps

- SATA 3.0 Host and SATA Device x2 (SATA connector x4)

- High Pin Count FMC Connector with transceivers. Support VADJ 1.2V/1.5V/1.8V only

- One Gigabit Ethernet Port

- On-Board 32-bit DDR4 with ECC

- DDR4 SO-DIMM Socket with ECC (up to 1066.667 MHz)

- Accelerometer, Gyroscope, Magnetometer (MPU9250)

- EPCQ1024L Serial Flash for Configuration and User Data

- Fixed and Programmable clock source for user logic, user interface, transceiver and memory

- Temperature Sensor,I2C Fan Control

- SMA Clock-In and Clock-Out.Support 1.8V I/O Standard

- LED x2, KEY x2, Switch x2, 7-Segment x2

- HPS(Hard Processor System)

- Boost Flash Slot for booting daughter card:1024 Mb QSPI Flash, NAND flash, MicroSD Socket

- DDR4 SO-DIMM Socket with ECC (up to 1066.667 MHz)

- Giga Ethernet with RJ45 connector

- USB OTG,Mini-AB USB connector

- UART-to-USB,Mini-B USB connector

- RTC

- LED x1, KEY x1

- Cold Reset and Warm Reset

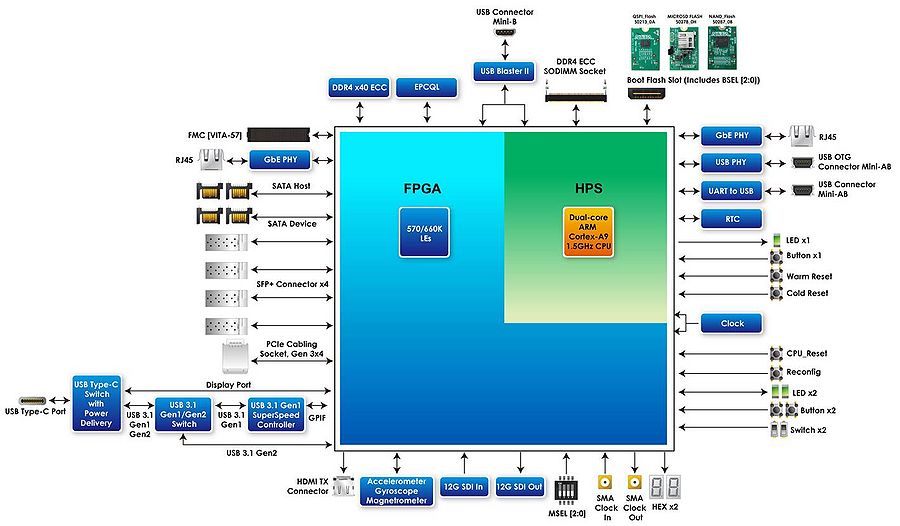

Block Diagram of the DE10-Advanced Board

Figure 2-3 is the block diagram of the board. All the connections are established through the Arria 10 SoC FPGA device to provide maximum flexibility for users. Users can configure the FPGA to implement any system design.

- Figure 2-2 Block diagram of DE10-Advanced

Detailed information about Figure 2-2 are listed below.

Arria 10 SoC 10AS066K3F40E2SG/10AS057K3F40E2SG FPGA

- Dual-core ARM Cortex-A9 (HPS)

- 660K programmable logic elements

- 42,660 Kbits embedded memory

- Hard memory controllers x5

- Transceivers x48(17.4 Gbps)

- 18-bit x 19-bit multipliers x3,356

- Accelerometer & Gyroscope Device MPU9250

Configuration

- EPCQ512 Serial Configuration Device

- Onboard USB-Blaster II (Mini-B USB connector)

Memory Device

- 32GB DDR4 SDRAM on FPGA

- Two DDR3 SO-DIMM SDRAM socket

- Micro SD card socket

- 1024Mb QSPI Flash

Communication

- USB OTG (Mini-AB USB connector)

- UART-to-USB (Mini-B USB Connector)

- Giga Ethernet x2

- PCIe Gen3 x4 Cabling Socket

FMC connector

- one HPC(high-pin count) FMC connector with xcvr

- Adjustable VADJ:1.2V/1.5V/1.8V

- FMC Vita57.1 Standard

SDI connectors

- Two 12G-SDI connectors for SDI in and out

SMA connectors

- Two SMA connectors for SMA Clock-In and Clock-Out

- Support 1.8V I/O Standard

General user input/output

- Buttons x3 (FPGA x2, HPS x1)

- Switches x2 on FPGA

- LEDs x3 (FPGA x2, HPS x1)

- 7-segment displays x2

System Monitor and Control

- Temperature Sensor on FPGA

- 12V Power Monitor

- Power Controller

- I2C Fan Control

Power

- 12V DC input

Chapter 3 Board Setting and Status component

Header

Switches

LED

Chapter 4 FPGA Fabric component

USB Type C Port

The board has one USB type C port with a EZ-PD CCG3 controller,the EZ-PD CCG3 device is available in 40-QFN and 42-WLCSP packages.

Gigabit Ethernet

The development board supports an RJ-45 10/100/1000 base-T Ethernet using Micrel KSZ9031MNX PHY.The KSZ9031MNX chip with integrated 10/100/1000 Mbps Gigabit Ethernet transceiver also supports GMII/MII MAC interface.For detailed information on how to use the KSZ9031MNX refers to its datasheet and application notes, which are available on the manufacturer’s website. There are two LEDs, green LED (LEDG) and yellow LED (LEDY), which represent the status of Ethernet PHY (KSZ9031MNX). The LED control signals are connected to the LEDs on the RJ45 connector. For instance, the connection from board to Gigabit Ethernet is established once the LEDG lights on.

Signal Name FPGA Pin No. Description I/O Standard ETH_TX_p PIN_AP19 LVDS ETH_RX_p PIN_AM20 LVDS ETH_INT_n PIN_AU19 1.8V ETH_MDC PIN_AT19 1.8V ETH_MDIO PIN_AJ20 1.8V ETH_RST_n PIN_AK20 1.8V

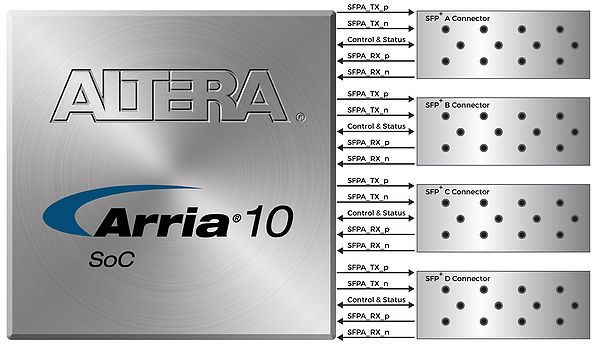

SFP+ Connector

The development board has four independent 10G SFP+ connectors that use one transceiver channel each from the Arria 10 SoC FPGA device. These modules take in serial data from the Arria 10 SoC FPGA device and transform them to optical signals. The board includes cage assemblies for the SFP+ connectors.Figure 4-1 shows the connections between the SFP+ and Arria 10 SoC FPGA.

Table 4-1, Table 4-2, Table 4-3 and Table 4-4 list the four QSF+ connectors assignments and signal names relative to the Arria 10 SoC FPGA

- Table 4-1 SFP+ A Pin Assignments, Signal Names and Functions

Signal Name FPGA Pin No. Description I/O Standard SFPA_TXDISABLE PIN_W28 Turns off and disables the transmitter output 1.2 V SFPA_TXFAULT PIN_T28 Transmitter fault 1.2 V SFPA_TX_p PIN_AG37 Transmiter data HSSI DIFFERENTIAL I/O SFPA_RX_p PIN_AD35 Receiver data HSSI DIFFERENTIAL I/O SFPA_LOS PIN_G27 Signal loss indicator 1.2 V SFPA_MOD0_PRSNT_n PIN_K27 Module present 1.2 V

- Table 4-2 SFP+ B Pin Assignments, Signal Names and Functions

Signal Name FPGA Pin No. Description I/O Standard SFPB_TXDISABLE PIN_B22 Turns off and disables the transmitter output 1.2 V SFPB_TXFAULT PIN_F15 Transmitter fault 1.2 V SFPB_TX_p PIN_AF39 Transmiter data HSSI DIFFERENTIAL I/O SFPB_RX_p PIN_AC37 Receiver data HSSI DIFFERENTIAL I/O SFPB_LOS PIN_K16 Signal loss indicator 1.2 V SFPB_MOD0_PRSNT_n PIN_Y27 Module present 1.2 V

- Table 4-3 SFP+ C Pin Assignments, Signal Names and Functions

Signal Name FPGA Pin No. Description I/O Standard SFPC_TXDISABLE PIN_AN6 Turns off and disables the transmitter output 1.2 V SFPC_TXFAULT PIN_AE10 Transmitter fault 1.2 V SFPC_TX_p PIN_AE37 Transmiter data HSSI DIFFERENTIAL I/O SFPC_RX_p PIN_AC33 Receiver data HSSI DIFFERENTIAL I/O SFPC_LOS PIN_AW3 Signal loss indicator 1.2 V SFPC_MOD0_PRSNT_n PIN_AP3 Module present 1.2 V

- Table 4-4 SFP+ D Pin Assignments, Signal Names and Functions

Signal Name FPGA Pin No. Description I/O Standard SFPD_TXDISABLE PIN_M1 Turns off and disables the transmitter output 1.2 V SFPD_TXFAULT PIN_M4 Transmitter fault 1.2 V SFPD_TX_p PIN_AD39 Transmiter data HSSI DIFFERENTIAL I/O SFPD_RX_p PIN_AB35 Receiver data HSSI DIFFERENTIAL I/O SFPD_LOS PIN_T2 Signal loss indicator 1.2 V SFPD_MOD0_PRSNT_n PIN_V7 Module present 1.2 V SFP_REFCLK_p PIN_AD31 SFP reference clock LVDS SFP_MOD1_SCL PIN_AK26 Serial 2-wire clock 1.2 V SFP_MOD2_SDA PIN_AE25 Serial 2-wire data 1.2 V

SATA

The four Serial ATA (SATA) ports are available on the FPGA development board which are computer bus standard with a primary function of transferring data between the motherboard and mass storage devices (such as hard drives, optical drives, and solid-state disks). Supporting a storage interface is just one of many different applications for which an FPGA can be used in storage appliances. The Arria 10 SoC device can bridge different protocols such as bridging simple bus I/Os like PCI Express (PCIe) to SATA or network interfaces such as Gigabit Ethernet (GbE) to SATA.

The SATA interface supports SATA 3.0 standard with connection speed of 6 Gbps based on Arria 10 SoC device with integrated transceivers compliant to SATA electrical standards.

The two Serial ATA (SATA) ports include one available port for device and one available port for host capable of implementing SATA solution with a design that consists of both host and target (device side) functions.Figure 4-1 shows the connections between the SATA and Arria 10 SoC FPGA. Table 4-1 list the SATA pin assignments and signal names relative to the Arria 10 SoC FPGA.

Signal Name FPGA Pin Number Description I/O Standard SATA_HOST_REFCLK_p PIN_V31 SATA Host reference clock LVDS SATA_HOST_TX_p[0] PIN_P39 SATA Host transmitter data p[0] HSSI DIFFERENTIAL I/O SATA_HOST_TX_p[1] PIN_N37 SATA Host transmitter data p[1] HSSI DIFFERENTIAL I/O SATA_HOST_RX_p[0] PIN_U33 SATA Host Receiver data p[0] HSSI DIFFERENTIAL I/O SATA_HOST_RX_p[1] PIN_T35 SATA Host Receiver data p[1] HSSI DIFFERENTIAL I/O SATA_DEVICE_REFCLK_p PIN_M31 SATA Device reference clock LVDS SATA_DEVICE_TX_p[0] PIN_B39 SATA Device transmitter data p[0] HSSI DIFFERENTIAL I/O SATA_DEVICE_TX_p[1] PIN_A37 SATA Device transmitter data p[1] HSSI DIFFERENTIAL I/O SATA_DEVICE_RX_p[0] PIN_D35 SATA Device Receiver data p[0] HSSI DIFFERENTIAL I/O SATA_DEVICE_RX_p[1] PIN_B35 SATA Device Receiver data p[1] HSSI DIFFERENTIAL I/O

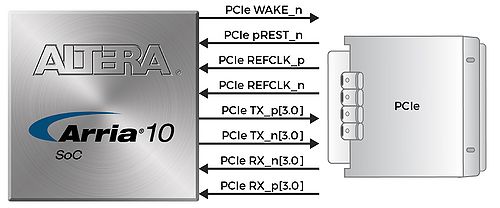

PCIe

The DE10-Advanced development board features one PCIe Express downstream interfaces (x4 lane) which are designed to interface with a PC motherboard x4 slot via PCIe cable and PCIe adapter card. Utilizing built-in transceivers on a Arria 10 SoC device, it is able to provide a fully integrated PCI Express compliant solution for multi-lane (x4) applications. With the PCI Express hard IP block incorporated in the Arria 10 SoC device, it will allow users to implement simple and fast protocols, as well as saving logic resources for logic applications.

The PCI Express interface supports complete PCI Express Gen1 at 2.5Gbps/lane, Gen2 at 5.0Gbps/lane, and Gen3 at 8.0Gbps/lane protocol stack solution compliant to PCI Express base specification 3.0 that includes PHY-MAC, Data Link, and transaction layer circuitry embedded in PCI Express hard IP blocks.

To use PCIe interface, two external associated devices will be needed to establish a link with PC. First, a PCIe half-height add-in host card with a PCIe x4 cable connector called PCA (PCIe Cabling Adapter Card and see picture below)will be used to plug into the PCIe slot on a mother board.

Then,a PCIe x4 cable(See picture below) will be used to connect DE10-Advanced board and PCIe add-in card, the longest length is up to 3 meters.

PCI Express Pin Connection is showed below.

These two associated devices are not included in DE10-Advanced board. To purchase the PCA card as well as the external cable, please refer to Terasic website pca.terasic.com and PCIe_Cable.terasic.com.Below table summarizes the PCI Express pin assignments of the signal names relative to the Arria 10 SoC FPGA.

Signal Name FPGA Pin Number Description I/O Standard PCIE_REFCLK_p PIN_AH31 PCIe reference clock LVDS PCIE_TX_p[0] PIN_AR37 PCIe Transmitter data p0 HSSI DIFFERENTIAL I/O PCIE_TX_p[1] PIN_AP39 PCIe Transmitter data p1 HSSI DIFFERENTIAL I/O PCIE_TX_p[2] PIN_AN37 PCIe Transmitter data p2 HSSI DIFFERENTIAL I/O PCIE_TX_p[3] PIN_AM39 PCIe Transmitter data p3 HSSI DIFFERENTIAL I/O PCIE_RX_p[0] PIN_AL33 PCIe Receiver data p0 HSSI DIFFERENTIAL I/O PCIE_RX_p[1] PIN_AM35 PCIe Receiver data p1 HSSI DIFFERENTIAL I/O PCIE_RX_p[2] PIN_AJ33 PCIe Receiver data p2 HSSI DIFFERENTIAL I/O PCIE_RX_p[3] PIN_AK35 PCIe Receiver data p3 HSSI DIFFERENTIAL I/O PCIE_PERST_n PIN_AW20 PCIe present,active low 1.8 V PCIE_WAKE_n PIN_AL19 PCIe wake 1.8 V

DDR4 SO-DIMM Socket

The development board supports DDR4 SDRAM SO-DIMM. The DDR4 SODIMM socket is wired to support a maximum capacity of 8GB with a 64-bit data bus. Using differential DQS signaling for the DDR4 SDRAM interfaces, it is capable of running at up to 1067MHz memory clock. It also supports Terasic QDRII+ module and RLDRAM3 module.Figure 2-12 shows the connections between the DDR4 SDRAM SO-DIMM and Arria 10 SoC FPGA.

HDMI

The development board provides High Performance HDMI Transmitter via the devices SN75DP159 which incorporates HDMI v1.4b and v2.0a features, including Ultra HD video and HDTV support. The SN75DP159 is controlled via a serial I2C bus interface, which is connected to pins on the Arria 10 SoC FPGA.The pin assignment associated to HDMI port is listed in table below.

Signal Name FPGA Pin Number Description I/O Standard HDMI_REFCLK_p PIN_Y31 LVDS HDMI_TX_CLK_p PIN_V39 HSSI DIFFERENTIAL I/O HDMI_TX_D_p[0] PIN_U37 HSSI DIFFERENTIAL I/O HDMI_TX_D_p[1] PIN_T39 HSSI DIFFERENTIAL I/O HDMI_TX_D_p[2] PIN_R37 HSSI DIFFERENTIAL I/O

Display Port

The DE10-Advanced board includes a DisplayPort connector. Molex 0.50mm pitch DisplayPort male receptacle, right angle, surface mount, 0.76µm gold plating, 20 circuits with cover.