Ax5soc Board Revision Document

From Terasic Wiki

Contents |

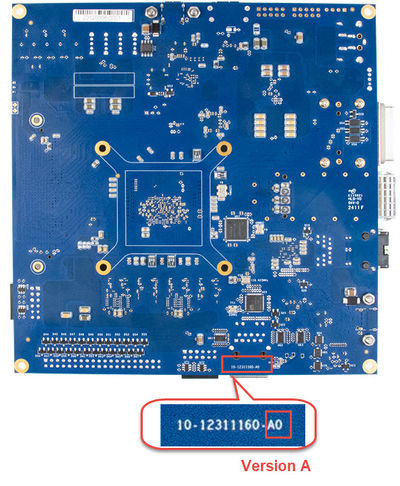

How to Find the Atum A5 Development Kit Revision?

On the bottom view of the PCB, there is a seal mark for the board hardware version.

As shown in the figure below, if the letter inside the red circle is "A", it means that the PCB version is Rev.A.

Board Revision Details

Version Difference Report: From Version A to Version B

- Fix eMCC issue, it can work on Version B

- Power Switch SW5 Label Correction

- The on/off label for SW5 in Version A was incorrect. In Version B, this has been corrected

- SD/eMMC Interface Modification

- Changed the SD/eMMC interface to a 4-bit connection.

- Reassigned the unused HPS IO pins to connect the HPS JTAG.

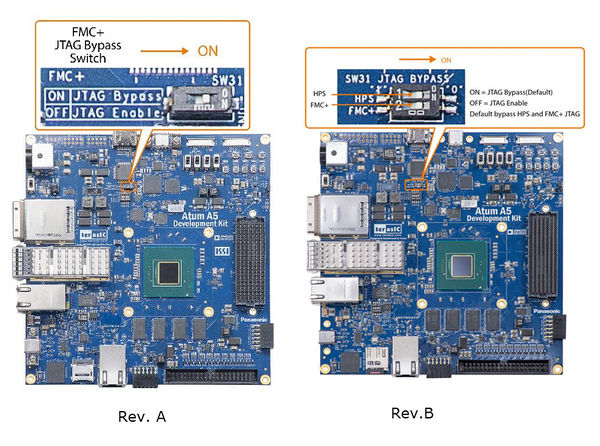

- Modify JTAG Switch SW31

- Replaced SW31 with a 2-channel DIP switch(add HPS JTAG bypass function).

- Added the HPS_JTAG_BYPASS_n pin in MAX 10.

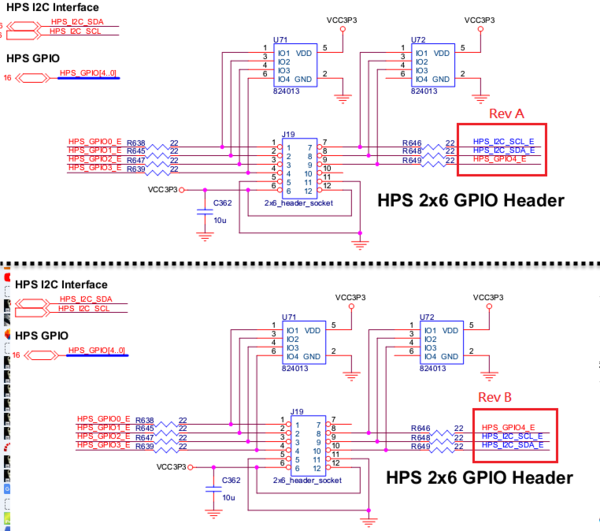

- HPS 2x6 GPIO Header Pin Assignment Change

- Updated the HPS 2x6 GPIO Header pin assignment.

- The new assignment includes one SPI.

Version Difference Report: From Version B to Version C

- USB Blaster Circuit Upgrade: Upgraded the on-board debugger from USB Blaster II to USB Blaster III

- USB-to-UART Bridge Integration: Removed the legacy 3-port USB HUB and the standalone Silicon Labs CP2105 USB-to-UART chip

- The dual USB-to-UART interfaces (for the HPS and System MAX10) are now directly handled by the FTDI chip (FT2232H) integrated within the USB Blaster III circuit

- Status LED Modification: Removed the dedicated single-color LEDs for JTAG_TX (D6) and JTAG_RX (D5)

- Replaced them with a new consolidated RGB LED (LED4 / JTAG_Blaster_LED) to indicate the comprehensive USB Blaster III operating status

- Change “Power chip set” to “MPS”