DE1-SoC Rev.G to Rev.H Revision List

From Terasic Wiki

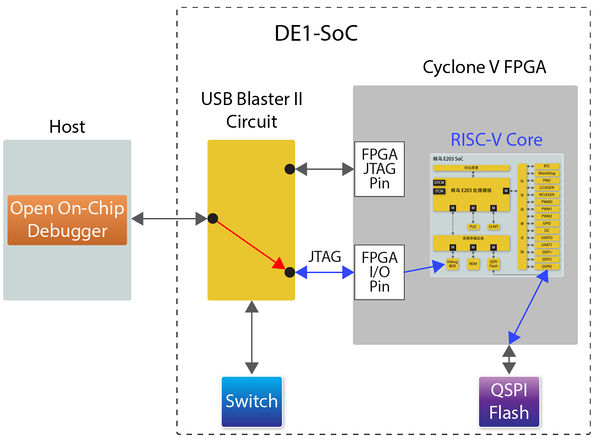

In rev.H, the DE1-SoC adds some features for supporting RISC-V application such as QSPI flash, UART to USB for FPGA and JTAG switch. Below are the change list for rev. G to rev. H.

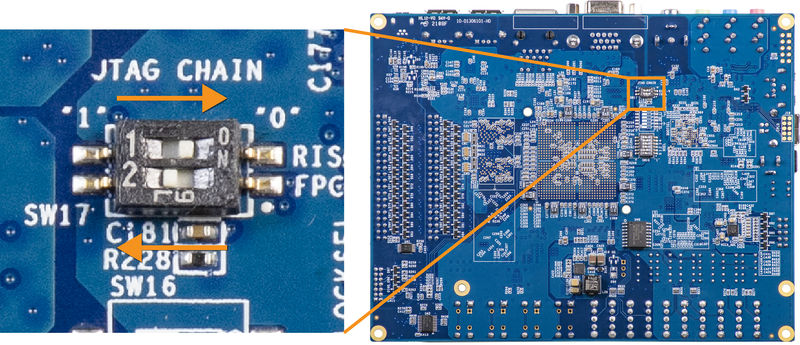

- Adding JTAG switch(SW17) for switch JTAG chain to FPGA JTAG pin or FPGA I/O(for RISC-V application).

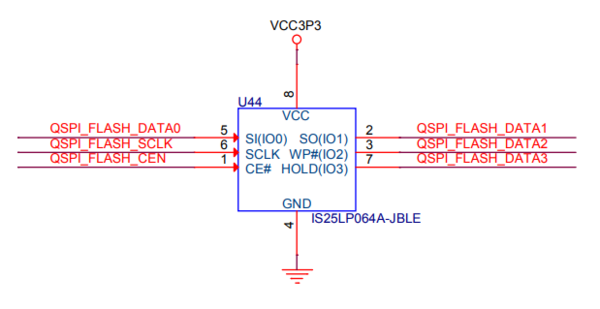

- Adding a 64M-bit serial NOR flash device (ISSI: IS25LP064A) for non-volatile storage, this QSPI Flash can store the software binary file of the RISC-V applications.

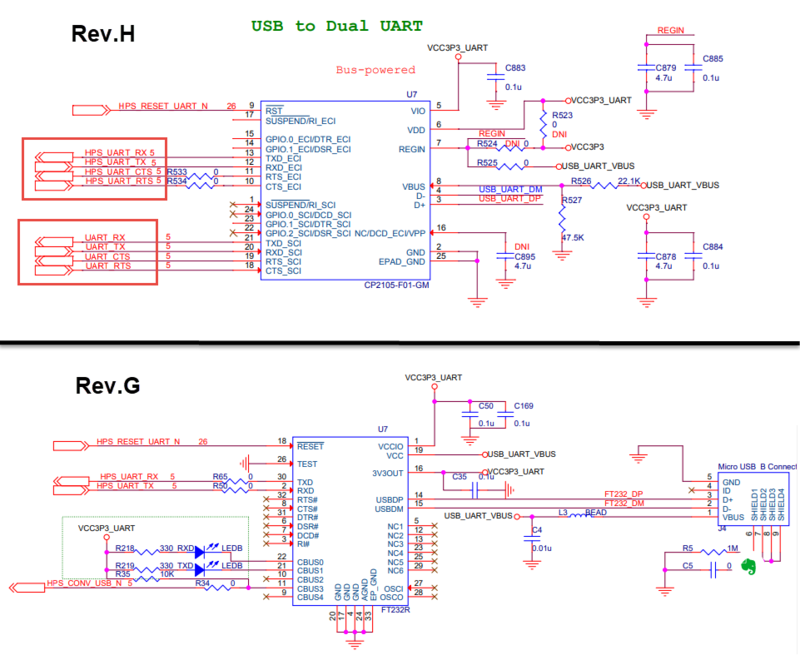

- Modify the UART to USB interface, using Silicon labs CP2105 dual UART bridge to replace FT232R. The CP2105 can provides two UART interface to the Cyclone V SoC FPGA, the HPS fabric and FPGA can both get the UART interface to the Host.

- Modify the CPLD device of the USB Blaster, from MAX II to MAX10 FPGA.