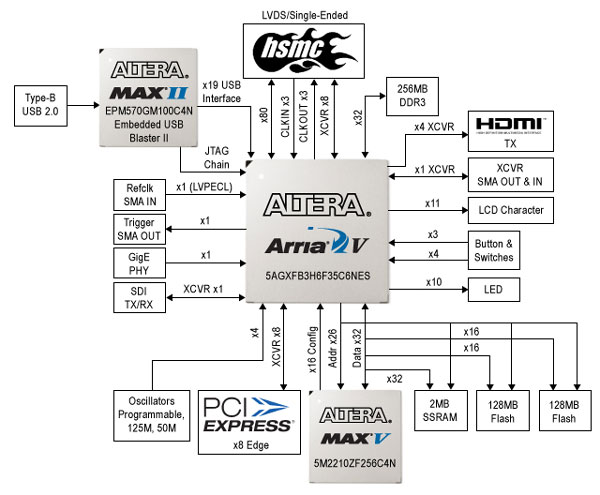

FPGA:

- Arria V GX 5AGXFB3H4F35C4N

系统控制: MAX® V 5M2210ZF256C4N

- 电源监测图形用户界面

- 单个模数转换器, 八通道

- 非隔离电源轨

- 通过并行闪存加载器(PFL)实现快速被动并行(FPP)x16模式

- 控制和状态寄存器

嵌入式USB Blaster II:

- MAX II EPM570GM100C4N

HDMI 1.3 TX

- x4 XCVR, 2.7 Gbps (通过电平转换器实现的最大值), 270 MHz TX时钟,HDMI TX连接头

- 意法半导体HDMI电平转换器--STHDLS101T

- 电平转换XCVR PCML 1.5V <-> TMDS电平

- DDC和HPD <-> 兼容HDMI电平

- 最高达2.7Gbps数据传输通道; HDMI 1.3兼容

- 最高270MHz的时钟通道; 足够支持2.7Gbps数据传输

- 电平转换XCVR PCML 1.5V <-> TMDS电平

SDI 3G

- 1 个XCVR TX/RX回环

- 2个SMB连接头和线缆 (线缆不包含在开发板套件内)

- 最高达2.97 Gbps

- 使用美国国家半导体公司的驱动/接收器 LMH0384SQ/LMH0303SQx

- 需要148.5 MHz 和148.35 MHz的XCVR 参考时钟,分别支持美规和欧规

- 使用VCXO微调并锁定恢复的CDR频率

HSMC

- 8个XCVR,最高达6.375 Gbps

- 不符合PCIExpress®(PCIe®)HIP引脚分配

- 4个CMOS

- 8个TX 和9个RX差分接口,使用专用的TX/RX通道

- 2个 低压差分信号(LVDS)时钟输入

- 2个 差分时钟输出

- I2C

- JTAG

- 支持的最小电压

- 2A @ 3.3V

- 1A @ 12V

- 从Si 5338 时钟生成器提供给 xcvr refclk 的专用时钟域

- 有BTS GUI可测试HSMC回环

SMA

- 1个 XCVR TX/RX 通道

- 1个 LVPECL 时钟输入

- 1个 LVPECL 时钟输出

时钟

- 从Si 5338时钟生成器提供给 xcvr refclk 的专用时钟域

DDR3 SDRAM x32

- Micron MT41J64M16LA-15E DDR3 SDRAM 8MX16X8

- 2个芯片,位宽是 2 x16 bit = 32位

- BTS DDR3 SDRAM GUI,使用 Uniphy 和高性能 (HP) 控制器 II

SSRAM

- 512k x36, 18 Mb ISSI IS61VPS51236A

- 与 flash 共享地址或数据

用户IO

- LCD 字符显示器

- DIP 开关4个

- PB 3个

- LED 4个

配置

- FPP x16 模式

- 双 flash, 芯片 Numonyx PC28F512P30BF,512Mbit (最大频率 52 MHz

- JTAG 插头

内嵌 USB Blaster II下载电路

- Cypress 的微控制器 CY7C68013A 做为USB PHY 2.0

- MAX II

以太网

- 10/100/1000 Base-T

- RJ-45 连接器, 板载 LED 指示灯显示链路状态

- Marvell Ethernet PHY 88E1111

- 要求从CLKIN提供50MHz时钟

Intel Arria V GX Starter Board 功能框图