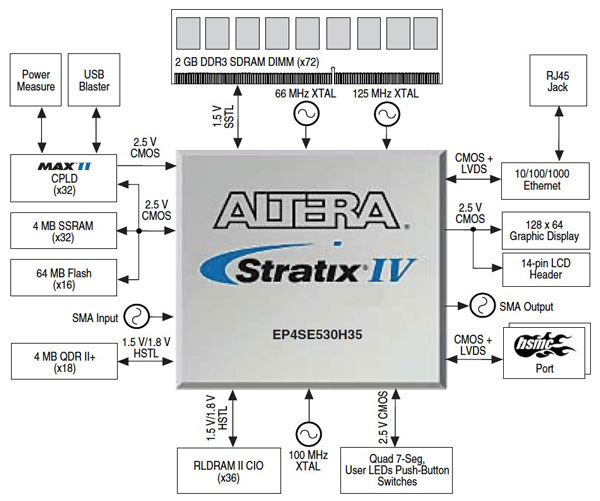

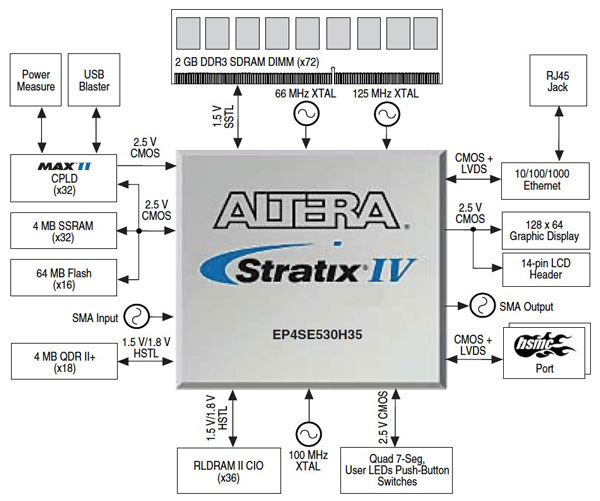

Altera Stratix IV E FPGA Development Kit

Featured device

- Stratix IV E EP4SE530H35C2N FPGA

Configuration, status, and set-up elements

- Fast passive parallel (FPP) configuration via a MAX®

II EPM2210 CPLD and flash memory

- On-board USB-BlasterTM

download cable using Quartus II Programmer

Clocks

- On-board clock oscillators: 50 MHz, 66 MHz, 100 MHz, and 125 MHz

- SMA connectors for external clock input

- SMA connector for clock output

General user input and output

- LEDs

- Push buttons

- Dual in-line package (DIP) switches

- Graphics LCD

- Character LCD

- Quad seven-segment display

Memory devices

- 2-GB DDR3 SDRAM DIMM with a 72-bit data bus

- 72-MB QDR II+ SRAM device with a 18-bit data bus

- 576-MB RLDRAM II CIO device with a 36-bit data bus

- 18-MB SSRAM with a 36-bit data bus

- 512-MB flash memory with a 16-bit data bus

Components and interfaces

- Two HSMC connectors

- 10/100/1000BASE-T Ethernet PHY with RJ-45 connector

- Temperature measurement circuitry

- Power measurement circuitry

Other features

- Restricted of hazardeous substances (RoHS) compliant

- 8.25” x 7” Board

- Bench-top design

Altera Stratix IV E FPGA Development Board Block Diagram