USER MANUAL

terasic www.terasic.com Copyright © 2003-2016 Terasic Inc. All Rights Reserved.

tron

| CHAPTER 1     | OVERVIEW                                    | 4  |

|---------------|---------------------------------------------|----|

| 1.1 General   | Description                                 | 4  |

| 1.2 Key Feat  | TURES                                       | 4  |

| 1.3 Block D   | DIAGRAM                                     | 6  |

| CHAPTER 2     | BOARD COMPONENTS                            | 9  |

| 2.1 BOARD C   | Overview                                    | 9  |

| 2.2 Configu   | IRATION, STATUS AND SETUP                   |    |

| 2.3 GENERAL   | L User Input/Output                         |    |

| 2.4 TEMPERA   | ATURE SENSOR, FAN CONTROL AND POWER MONITOR |    |

| 2.5 Clock C   | IRCUIT                                      |    |

| 2.6 FLASH A   | AND SSRAM MEMORY                            |    |

| 2.7 DDR3 S0   | O-DIMM                                      |    |

| 2.8 FMC Cor   | NNECTORS                                    |    |

| 2.9 SATA      |                                             |    |

| 2.10 GPIO     |                                             | 41 |

| 2.11 PCI EXP  | PRESS                                       | 44 |

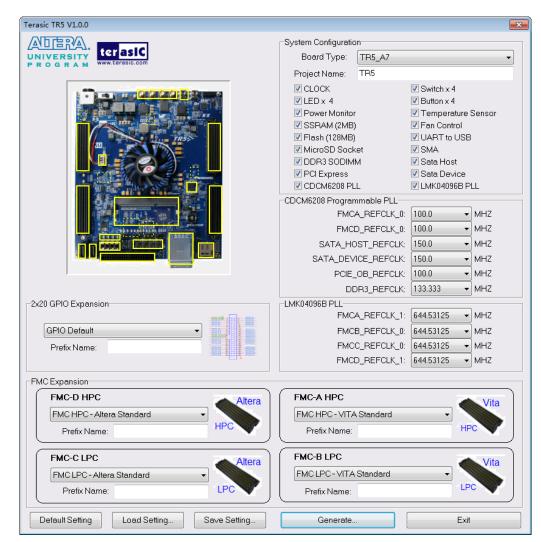

| CHAPTER 3     | SYSTEM BUILDER                              |    |

| 3.1 Introdu   | ICTION                                      |    |

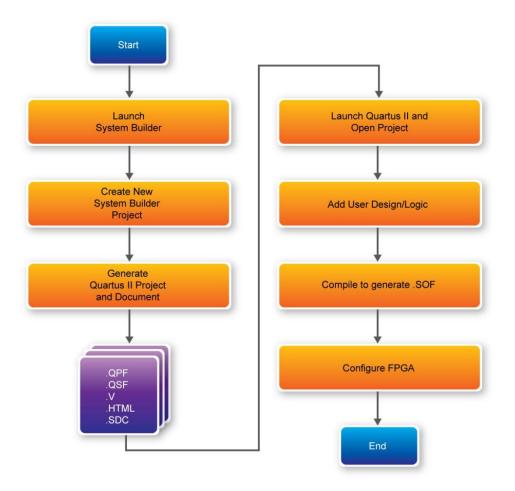

| 3.2 GENERAL   | L DESIGN FLOW                               |    |

| 3.3 USING SY  | YSTEM BUILDER                               |    |

| CHAPTER 4     | FLASH PROGRAMMING                           | 60 |

| 4.1 CFI FLAS  | SH MEMORY MAP                               |    |

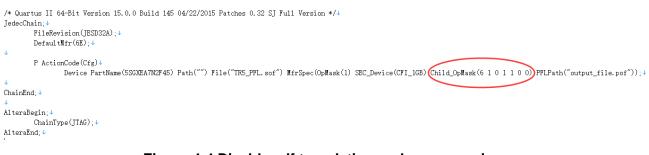

| 4.2 FPGACo    | ONFIGURE OPERATION                          | 61 |

| 4.3 Flash Pf  | ROGRAMMING WITH USERS DESIGN                |    |

| 4.4 Restore   | FACTORY SETTINGS                            |    |

| CHAPTER 5     | PROGRAMMABLE PLL                            |    |

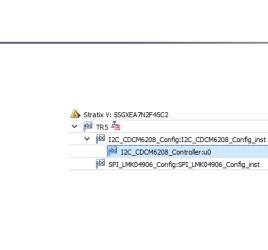

| 5.1 Configu   | IRE CDCM6208 AND LMK04096B IN RTL           |    |

| 5.2 Nios II c | ONTROL FOR PLL/TEMPERATURE/POWER            |    |

| CHAPTER 6     | EXAMPLES OF ADVANCED DEMONSTRATION |  |

|---------------|------------------------------------|--|

| 6.1 Flash and | D SSRAM TEST                       |  |

| 6.2 DDR3 SD   | RAM TEST                           |  |

| 6.3 DDR3 SD   | RAM TEST BY NIOS II                |  |

| 6.4 FAN SPEEI | O CONTROL                          |  |

| 6.5 UART то   | USB Control                        |  |

| CHAPTER 7     | PCI EXPRESS REFERENCE DESIGN       |  |

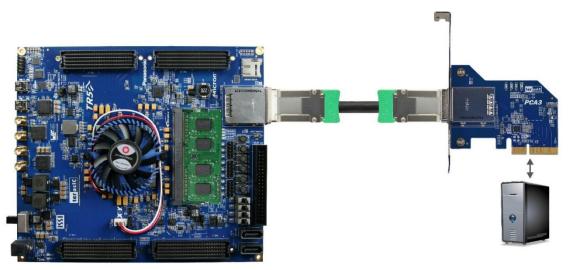

| 7.1 PCI Expri | ess System Infrastructure          |  |

| 7.2 PC PCI Ex | XPRESS SOFTWARE SDK                |  |

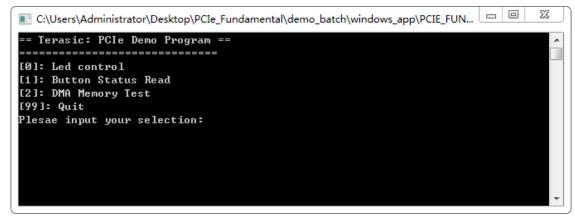

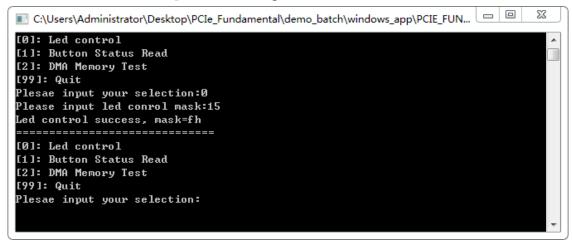

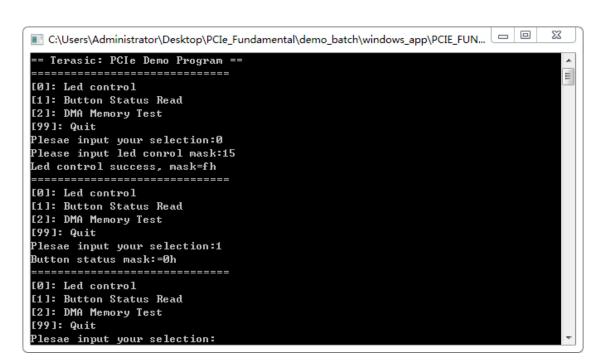

| 7.3 REFERENCE | e Design - Fundamental             |  |

| 7.4 PCIE REF  | ERENCE DESIGN – DDR3               |  |

| CHAPTER 8     | TRANSCEIVER VERIFICATION           |  |

| 8.1 FUNCTION  | OF THE TRANSCEIVER TEST CODE       |  |

| 8.2 FUNCTION  | OF THE TRANSCEIVER TEST CODE       |  |

| 8.1 TESTING   |                                    |  |

| CHAPTER 9     | FMC CONNECTORS PIN OUT             |  |

| ADDITIONAL I  | NFORMATION                         |  |

This chapter provides an overview of the TR5 Development Board and installation guide.

## **1.1 General Description**

The Terasic TR5 Stratix V GX FPGA Development Kit provides the ideal hardware solution for designs that demand high capacity and bandwidth interface, ultra-low latency communication, high pin count and power efficiency. With an iPass PCIe gen3 connector, the TR5 is designed for the most demanding high-end applications, empowered with the Altera 28 nm Stratix V GX, delivering the best system-level integration and flexibility in the industry.

The Stratix® V GX FPGA features integrated transceivers that transfer at a maximum of 12.5Gbps, this allows the TR5 to be fully compliant with version 3.0 of the PCI Express standard. Not relying on an external PHY will accelerate mainstream development of network applications enabling customers to deploy designs for a broad range of high-speed connectivity applications. For designs that demand high capacity and high speed for memory and storage, the TR5 delivers with one independent bank of DDR3 SO-DIMM RAM, one ZBT SSRAM, and high-speed parallel flash memory. The feature-set of the TR5 fully supports all high-intensity applications such as ASIC verification, data acquisition, and signal processing.

## **1.2 Key Features**

The following hardware is implemented on the TR5 board:

- FPGA

- Altera Stratix® V GX FPGA

- 5SGXEA7N2F45C2 /5SGXEABN3F45I3YY

- FPGA Configuration

- On-Board USB Blaster II or JTAG header for FPGA programming

- Fast passive parallel (FPPx16) configuration via MAX II CPLD and flash memory

- General user input/output:

- 4 LEDs

- 4 push-buttons

- 4 slide switches

- Clock System

- 50MHz Oscillator

- CDCM6208 Programmable PLL

- LMK04096B Programmable PLL

- SMA connector pairs for differential clock input and output

- Memory

- DDR3 SO-DIMM SDRAM

- QDRII+ SRAM

- FLASH

- SD Card

- Communication Ports

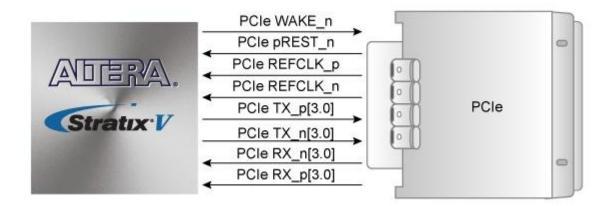

- PCI Express (PCIe) x4 iPass connector

- Serial ATA host and device ports

- PCI Express (PCIe) x8 edge connector

- One mini Uart to USB connector

- System Monitor and Control

- Temperature sensor

- Fan control

- Power monitor

- Mechanical Specification

- 4 FPGA Mezzanine Card (FMC) Connectors

- One 40-pin Expansion Header

- Power

• 12V DC Input

# **1.3 Block Diagram**

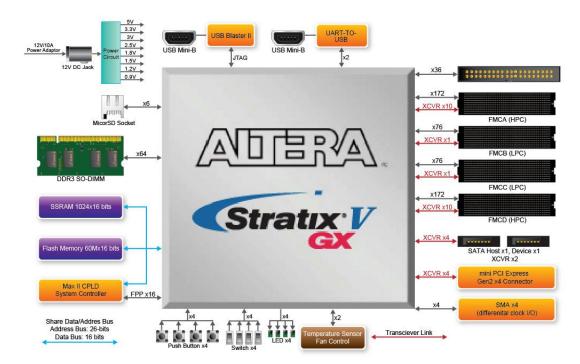

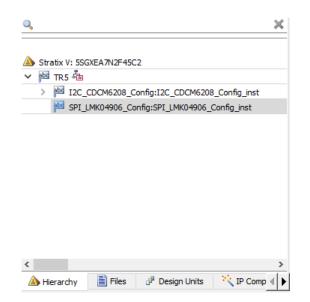

**Figure 1-1** shows the block diagram of the TR5 board. To provide maximum flexibility for the users, all key components are connected with the Stratix V GX FPGA device. Thus, users can configure the FPGA to implement any system design.

Figure 1-1 Block diagram of the TR5 board

Below is more detailed information regarding the blocks in Figure 1-1.

## Stratix V GX FPGA

- 5SGXEA7N2F45C2

- 622K logic elements (LEs)

- 57.16-Mbits embedded memory

- 48 transceivers (12.5Gbps)

- 512 18 x18 multipliers

- 256 Variable-precision DSP blocks

- 28 Fractional PLLs and 4DLLs

#### • 5SGXEABN3F45I3YY

- 952K logic elements (LEs)

- 62.96-Mbits embedded memory

- 48 transceivers (12.5Gbps)

- 704 18 x18 multipliers

- 352 Variable-precision DSP blocks

- 28 Fractional PLLs and 4DLLs

## JTAG Header and FPGA Configuration

- On-board USB Blaster II or JTAG header for use with the Quartus II Programmer

- MAXII CPLD EPM2210 System Controller and Fast Passive Parallel (FPP) configuration

## **Memory devices**

- 2MB ZBT SSRAM

- Up to 8GB DDR3 SO-DIMM SDRAM

- 256MB FLASH

## General user I/O

- 4 user controllable LEDs

- 4 user push buttons

- 4 user slide switches

## **On-Board Clock**

- 50MHz oscillator

- Programming PLL providing clock for FMC transceivers

- Programming PLL providing clock for PCIe transceiver

- Programming PLL providing clocks for DDR3 SDRAM

## **Two Serial ATA ports**

• SATA 3.0 standard at 6Gbps signaling rate

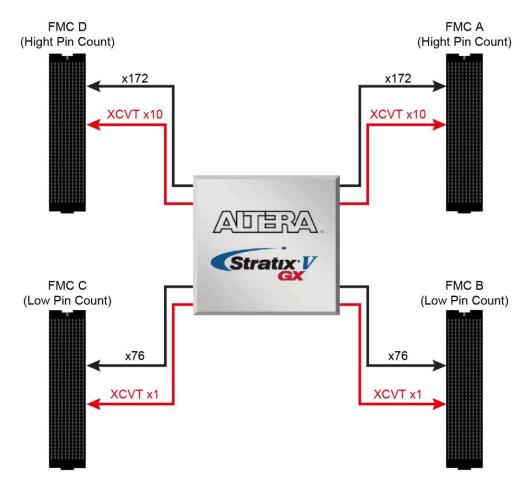

## **Four FMC Connectors**

- 2 HPC (high-pin count) FMC connectors up to 172 x2 Single-end I/O

- 2 LPC (low-pin count) FMC connectors up to 76 x2 Single-end I/O

- 10 Transceiver Channels for HPC and 1 Transceiver Channel for LPC

- FMC VITA 57.1 Compliant

- Adjustable VADJ: 1.2V/1.5V/1.8V/2.5V/3.0V

- Don't support bidirectional LVDS due to Stratix V device only support single directional LVDS

## **One 40-pin GPIO Expansion Header**

- 36 FPGA I/O pins; 4 power and ground lines

- I/O standards: 3.3V (with level shift from 2.5V to 3.3V)

## **External PCI Express x4 iPass Connector**

- Support for PCIe x4 Gen1/2/3

- iPass connector with x4 PCI Express slot

## **Power Source**

• DC 12V power adapter

# Chapter 2

# **Board Components**

This chapter introduces all the important components on the TR5.

# **2.1 Board Overview**

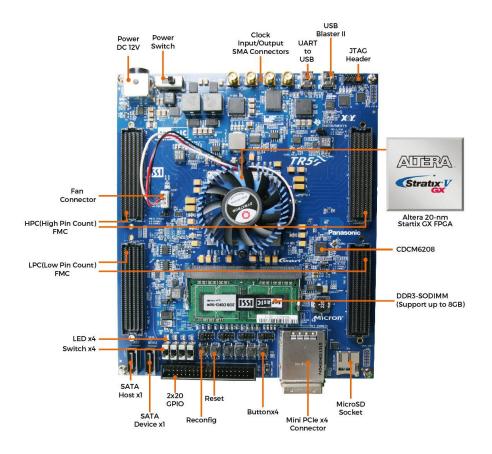

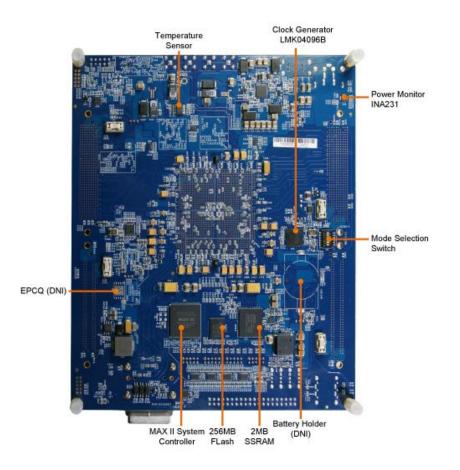

**Figure 2-1** is the top and bottom view of the TR5 development board. It depicts the layout of the board and indicates the location of the connectors and key components. Users can refer to this figure for relative location of the connectors and key components.

Figure 2-1 FPGA Board (Top)

Figure 2-2 FPGA Board (Bottom)

# **2.2 Configuration, Status and Setup**

#### ■ Configure

The FPGA board supports two configuration methods for the Stratix V FPGA:

- Configure the FPGA using the on-board USB-Blaster II.

- Flash memory configuration of the FPGA using stored images from the flash memory on power-up.

For programming by on-board USB-Blaster II, the following procedures show how to download a configuration bit stream into the Stratix V GX FPGA:

- Make sure that power is provided to the FPGA board.

- Connect your PC to the FPGA board using a mini-USB cable and make sure the USB-Blaster II driver is installed on PC.

- Launch Quartus II programmer and make sure the USB-Blaster II is detected.

- In Quartus II Programmer, add the configuration bit stream file (.sof), check the associated "Program/Configure" item, and click "Start" to start FPGA programming.

#### Status LED

The FPGA Board development board includes board-specific status LEDs to indicate board status. Please refer to **Table 2-1** for the description of the LED indicator.

| Board Reference | LED Name                       | Description                                                                                                                                                                               |  |  |  |

|-----------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D6              | 12-V Power                     | Illuminates when 12-V power is active.                                                                                                                                                    |  |  |  |

| D1              | 3.3-V Power                    | Illuminates when 3.3-V power is active.                                                                                                                                                   |  |  |  |

| D21             | CONF_DONE                      | Illuminates when the FPGA is successfully configured.<br>Driven by the MAX II CPLD EPM2210 System Controller.                                                                             |  |  |  |

| D22             | LOAD                           | Illuminates when the MAX II CPLD EPM2210 System<br>Controller is actively configuring the FPGA. Driven by<br>the MAX II CPLD EPM2210 System Controller with the<br>Embedded Blaster CPLD. |  |  |  |

| D23             | ERROR                          | Illuminates when the MAX II CPLD EPM2210 System<br>Controller fails to configure the FPGA. Driven by the<br>MAX II CPLD EPM2210 System Controller.                                        |  |  |  |

| D24             | BOOT_PAGE                      | Illuminates when FPGA is configured by the factory configuration bit stream.                                                                                                              |  |  |  |

| D12~D20,D33~D35 | FMC Voltage<br>Value Indicator | See Section 2.8 FMC Connectors                                                                                                                                                            |  |  |  |

| T | able | 2-1          | Status | I FD |

|---|------|--------------|--------|------|

| • | anic | <b>Z</b> - I | Jiaius |      |

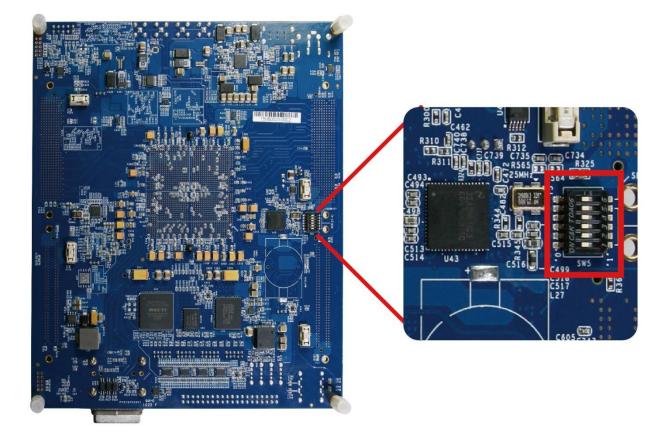

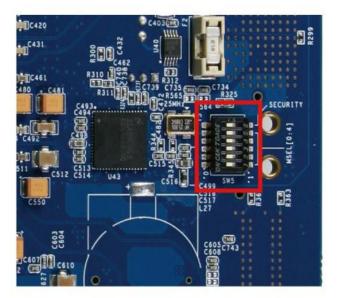

### Setup Configure Mode Control DIP switch

The Configure Mode Control DIP switch (SW5) is provided to specify the configuration mode of the FPGA. As currently only one mode is supported, please set all positions as shown in **Figure 2-3**.

Figure 2-3 4-Position DIP switch for Configure Mode

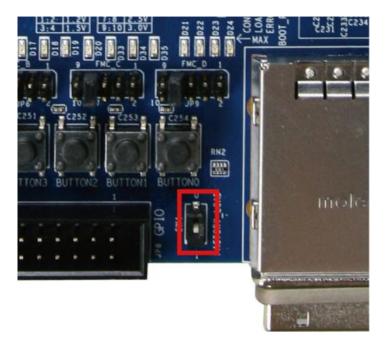

#### ■ Select Flash Image for Configuration

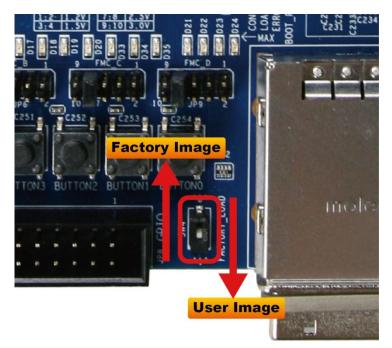

The Image Select DIP switch (SW4) is provided to specify the image for configuration of the FPGA. Setting SW4 to high ('0') specifies the default factory image to be loaded, setting SW4 to low ('1') specifies the TR5 to load a user-defined image, as shown in **Figure 2-4**.

Figure 2-4 2-position DIP switch for Image Select

#### ■ FMC VCCIO Voltage Setting Header

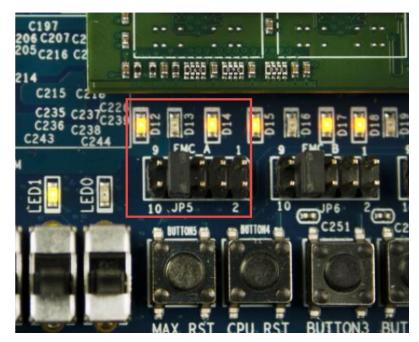

The I/O voltage of all the four FMC connectors is adjustable within 1.2/1.5/1.8/2.5/3.0V (\*1). For example, user can adjust the I/O voltage to 2.5V to support LVDS differential I/O stand. The user can control the voltage of FMCA~FMCD through JP5, JP6, JP7 and JP9. As shown in **Figure 2-5**, make short circuit onto JP5 pin 7 and pin 8, the status of D12, D13 and D14 will be set as "ON/OFF/ON" for representing the FMCA VCCIO is 2.5V. **Table 2-2**, **Table 2-3**, **Table 2-4** and **Table 2-5** lists the voltage settings of the FMCA~FMCD VCCIO and their corresponding LED display status.

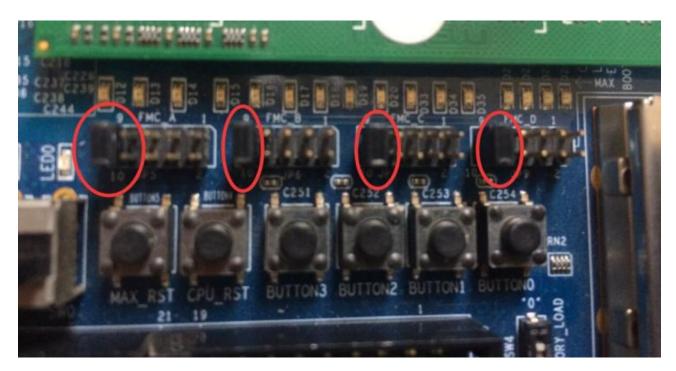

(\*1)Note: Because FMC connectors are cross connect to FPGA different banks, if users want to set individual FMC connector VCCIO to 3.0V, they need to set other three FMC connectors VCCIO to 3.0V too, otherwise the individual FMC connector VCCIO will be not 3.0V and the corresponding LEDs status is abnormal. **Figure 2-6** shows how to adjust the VCCIO: short Pin 9 & Pin 10 of JP5, JP6, JP7 and JP9

Figure 2-5 FMC A VCCIO Voltage Setting to 2.5V

Figure 2-6 Set individual FMC connector VCCIO to 3.0V (Short Pin 9 & Pin 10 of JP5, JP6, JP7 and JP9)

| JP5 Setting      |     | LED Status |     | FMC A VCCIO Voltage                                          |

|------------------|-----|------------|-----|--------------------------------------------------------------|

| JP5 Setting      | D12 | D13        | D14 | FINC A VCCIO Vollage                                         |

| Short Pin 1 & 2  | OFF | OFF        | ON  | 1.2V                                                         |

| Short Pin 3 & 4  | OFF | ON         | OFF | 1.5V                                                         |

| Short Pin 5 & 6  | OFF | ON         | ON  | 1.8V                                                         |

| Short Pin 7 & 8  | ON  | OFF        | ON  | 2.5V(Default)                                                |

| Short Pin 9 & 10 | ON  | ON         | OFF | 3.0V(Must to set other 3<br>FMC connectors VCCIO to<br>3.0V) |

#### Table 2-2 FMC A VCCIO Voltage Setting

#### Table 2-3 FMC B VCCIO Voltage Setting

| JP6 Setting      |     | LED Status | ;   | FMC B VCCIO Voltage                                 |

|------------------|-----|------------|-----|-----------------------------------------------------|

| JF0 Setting      | D15 | D16        | D17 | FINC B VCCIO Voltage                                |

| Short Pin 1 & 2  | OFF | OFF        | ON  | 1.2V                                                |

| Short Pin 3 & 4  | OFF | ON         | OFF | 1.5V                                                |

| Short Pin 5 & 6  | OFF | ON         | ON  | 1.8V                                                |

| Short Pin 7 & 8  | ON  | OFF        | ON  | 2.5V(Default)                                       |

| Short Pin 9 & 10 | ON  | ON         | OFF | 3.0V(Must to set other 3<br>FMC connectors VCCIO to |

|                  |     |            |     | 3.0V)                                               |

#### Table 2-4 FMC C VCCIO Voltage Setting

| ID7 Sotting      |     | LED Status | ;   |                                                              |

|------------------|-----|------------|-----|--------------------------------------------------------------|

| JP7 Setting      | D18 | D19        | D20 | FMC C VCCIO Voltage                                          |

| Short Pin 1 & 2  | OFF | OFF        | ON  | 1.2V                                                         |

| Short Pin 3 & 4  | OFF | ON         | OFF | 1.5V                                                         |

| Short Pin 5 & 6  | OFF | ON         | ON  | 1.8V                                                         |

| Short Pin 7 & 8  | ON  | OFF        | ON  | 2.5V(Default)                                                |

| Short Pin 9 & 10 | ON  | ON         | OFF | 3.0V(Must to set other 3<br>FMC connectors VCCIO to<br>3.0V) |

#### Table 2-5 FMC D VCCIO Voltage Setting

| IPO Sotting      |     | LED Status |     |                                                              |

|------------------|-----|------------|-----|--------------------------------------------------------------|

| JP9 Setting      | D33 | D34        | D35 | FMC D VCCIO Voltage                                          |

| Short Pin 1 & 2  | OFF | OFF        | ON  | 1.2V                                                         |

| Short Pin 3 & 4  | OFF | ON         | OFF | 1.5V                                                         |

| Short Pin 5 & 6  | OFF | ON         | ON  | 1.8V                                                         |

| Short Pin 7 & 8  | ON  | OFF        | ON  | 2.5V(Default)                                                |

| Short Pin 9 & 10 | ON  | ON         | OFF | 3.0V(Must to set other 3<br>FMC connectors VCCIO to<br>3.0V) |

#### ■ FMC JTAG Header

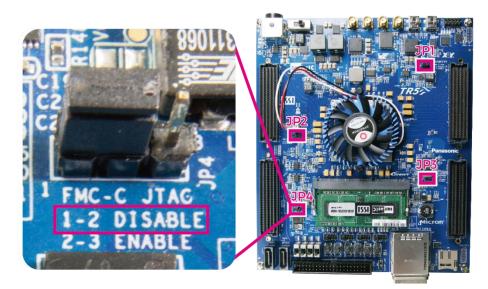

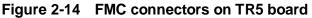

The TR5 supports individual JTAG interfaces on each FMC connector. This feature allows users to extend the JTAG chain to FMC daughter cards. The JTAG signals on each FMC connector can be removed or included in the active JTAG chain via 3-Pin header (See Figure 2-7). Table 2-6 lists the setting of the headers and their associated interfaces. Note that if the JTAG interface on FMC connector is enabled, make sure that the active JTAG chain must be a closed loop or the FPGA may not be detected.

Figure 2-7 FMCC JTAG Header

| Headers | Setting         | Description       |

|---------|-----------------|-------------------|

| JP1     | Short Pin 1 & 2 | Disable FMCA JTAG |

|         | Short Pin 2 & 3 | Enable FMCA JTAG  |

| IDO     | Short Pin 1 & 2 | Disable FMCD JTAG |

| JP2     | Short Pin 2 & 3 | Enable FMCD JTAG  |

| JP3     | Short Pin 1 & 2 | Disable FMCB JTAG |

| JFJ     | Short Pin 2 & 3 | Enable FMCB JTAG  |

| JP4     | Short Pin 1 & 2 | Disable FMCC JTAG |

| JF4     | Short Pin 2 & 3 | Enable FMCC JTAG  |

| Table 2- | 6 FMC | JTAG | Header | Setting |

|----------|-------|------|--------|---------|

|----------|-------|------|--------|---------|

# **2.3 General User Input/Output**

This section describes the user I/O interface to the FPGA.

#### ■ User Defined Push-buttons

The FPGA board includes four user defined push-buttons that allow users to interact with the Stratix V GX device. Each push-button provides a high logic level or a low logic level when it is not pressed or pressed, respectively. Table 2-7 lists the board references, signal names and their corresponding Stratix V GX device pin numbers.

| Board<br>Reference | Schematic<br>Signal Name | Description                         |       | Stratix V GX<br>Pin Number |

|--------------------|--------------------------|-------------------------------------|-------|----------------------------|

| BUTTON0            | BUTTON0                  | High Logic Level when the button is | 1.5-V | PIN_BC7                    |

| BUTTON1            | BUTTON1                  | not pressed                         | 1.5-V | PIN_BD7                    |

| BUTTON 2           | BUTTON2                  | -                                   | 1.5-V | PIN_BB8                    |

| BUTTON 3           | BUTTON3                  | -                                   | 1.5-V | PIN_BB9                    |

Table 2-7 Push-button Pin Assignments, Schematic Signal Names, and Functions

### ■ User-Defined Slide Switch

There are four slide switches on the FPGA board to provide additional FPGA input control. When a slide switch is in the DOWN position or the UPPER position, it provides a low logic level or a high

logic level to the Stratix V GX FPGA. The down position provides a low logic level and the upper position provides a high logic level.

Table 2-8 lists the signal names and their corresponding Stratix V GX device pin numbers.

| Board<br>Reference | Schematic<br>Signal Name | Description                           | I/O<br>Standard | Stratix V GX<br>Pin Number |

|--------------------|--------------------------|---------------------------------------|-----------------|----------------------------|

| SW0                | SW0                      | High logic level when SW in the UPPER | 1.5-V           | PIN_AT9                    |

| SW1                | SW1                      | position.                             | 1.5-V           | PIN_AU8                    |

| SW2                | SW2                      |                                       | 1.5-V           | PIN_AK9                    |

| SW3                | SW3                      |                                       | 1.5-V           | PIN_AL9                    |

Table 2-8 Slide Switch Pin Assignments, Schematic Signal Names, and Functions

#### User-Defined LEDs

The FPGA board consists of four user-controllable LEDs to allow status and debugging signals to be driven to the LEDs from the designs loaded into the Stratix V GX device. Each LED is driven directly by the Stratix V GX FPGA. The LEDs are turned on or off when the associated pins are driven to a low or high logic level, respectively. A list of the pin names on the FPGA that are connected to the LEDs is given in **Table 2-9**.

| Table 2-9 User LEDs Pin | Assignments  | Schematic Signa | I Names, and Functions  |

|-------------------------|--------------|-----------------|-------------------------|

|                         | Assignments, | Schematic Signa | i Names, and i unctions |

| Board<br>Reference | Schematic<br>Signal Name | Description                                     |       | Stratix V GX<br>Pin Number |

|--------------------|--------------------------|-------------------------------------------------|-------|----------------------------|

| LED0               | LED0                     | Driving a logic 0 on the I/O port turns the LED | 1.5-V | PIN_AT32                   |

| LED1               | LED1                     | ON.                                             | 1.5-V | PIN_BA31                   |

| LED2               | LED2                     | Driving a logic 1 on the I/O port turns the LED | 1.5-V | PIN_AN27                   |

| LED3               | LED3                     | OFF.                                            | 1.5-V | PIN_AH27                   |

### ■ UART-To-USB

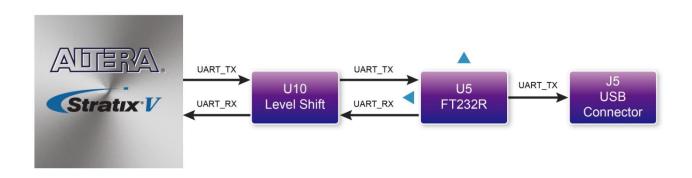

The UART is designed to perform communication between the board and the PC, allowing a transmission speed of up to 3Mbps. This interface wouldn't support HW flow control signals. The physical interface is done using UART-USB on-board bridge from a FT232R chip and connects to the host using a USB Type-B connector. For detailed information on how to use the transceiver, please refer to the datasheet, which is available on the manufacturer's website, or under the

Datasheets\FT232 folder on the Kit System CD. **Figure 2-7** shows the related schematics, and **Table 2-10** lists the UART pin assignments, signal names and functions.

Figure 2-8 Connection between UART-To-USB and Stratix V GX FPGA

| Ιαρια              | Table 2-10 OAR 1-10-03B Fill Assignments, Schematic Signal Names, and Functions |                          |                       |           |  |

|--------------------|---------------------------------------------------------------------------------|--------------------------|-----------------------|-----------|--|

| Schematic<br>Board |                                                                                 |                          |                       | Stratix V |  |

| Reference          | Signal                                                                          | Description              | I/O Standard          | GX Pin    |  |

| Nelelelica         | Name                                                                            |                          |                       | Number    |  |

| UART_TX            | UART_TX                                                                         | Uart TX output from FPGA | 1.2/1.5/1.8/2.5/3.0-V | PIN_T26   |  |

**Uart RX input to FPGA**

| Table 2-10 UART-To-USB Pin Ass | ignments, Schematic | Signal Names, | and Functions |

|--------------------------------|---------------------|---------------|---------------|

|--------------------------------|---------------------|---------------|---------------|

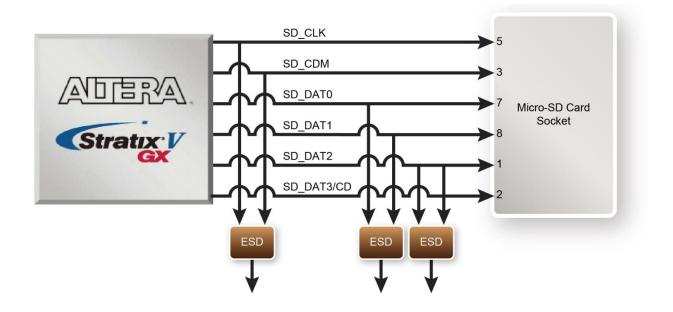

### Micro SD-Card

UART\_RX UART\_RX

The development board supports Micro SD card interface using 4 data lines. Figure 2-9 shows the related signals connections between the SD Card and Stratix V GX FPGA. Table 2-11 lists all the associated pins

1.2/1.5/1.8/2.5/3.0-V

PIN\_T25

Figure 2-9 Connection between the SD Card Socket and Stratix V GX FPGA

| Table 2-11 Micro SD Card Pin | Assignments  | Schomatic Sign  | al Namos   | and Eunctions |

|------------------------------|--------------|-----------------|------------|---------------|

|                              | Assignments, | Schematic Signa | ai maines, | and Functions |

| Schematic<br>Signal | Description       | I/O Standard | Stratix V<br>GX Pin |

|---------------------|-------------------|--------------|---------------------|

| Name                |                   |              | Number              |

| SD_CLK              | Serial Clock      | 1.5-V        | PIN_BB39            |

| SD_CMD              | Command, Response | 1.5-V        | PIN_BA36            |

| SD_DAT0             | Serial Data 0     | 1.5-V        | PIN_AV37            |

| SD_DAT1             | Serial Data 1     | 1.5-V        | PIN_AY37            |

| SD_DAT2             | Serial Data 2     | 1.5-V        | PIN_BB36            |

| SD_DAT3             | Serial Data 3     | 1.5-V        | PIN_AW37            |

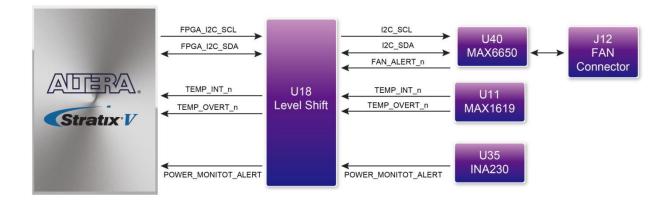

# 2.4 Temperature Sensor, Fan Control and Power Monitor

The FPGA board is equipped with a temperature sensor, MAX1619, which provides temperature sensing and over-temperature alert. These functions are accomplished by connecting the temperature sensor to the internal temperature sensing diode of the Stratix V GX device. The temperature status and alarm threshold registers of the temperature sensor can be programmed by a

two-wire <mark>SMBus</mark>, which is connected to the Stratix V GX FPGA. In addition, the 7-bit POR slave address for this sensor is set to '0011000b'.

A 3-pin +12V fan located on J12 of the FPGA board is intended to reduce the temperature of the FPGA. The board is equipped with a Fan-Speed regulator and monitor MAX6650 with an I2C/SMBus interfaces, Users regulate and monitor the speed of fan depending on the measured system temperature.

The TR5 has implemented a power monitor chip to monitor the board input power voltage and current. **Figure 2-10** shows the connection between the power monitor chip and the Stratix V GX FPGA. The power monitor chip monitors both shunt voltage drops and board input power voltage allows user to monitor the total board power consumption. Programmable calibration value, conversion times, and averaging, combined with an internal multiplier, enable direct readouts of current in amperes and power in watts. Note that, the temperature sensor, fan control and power monitor share the same I2C/SMBUS.

#### Figure 2-10 Connections between the temperature sensor/fan control/power monitor and the Stratix V GX FPGA

# Table 2-12 Temperature Sensor and Fan Speed Control Pin Assignments, Schematic SignalNames, and Functions

| Schematic<br>Signal Name | Description                                       | I/O Standard | Stratix V GX Pin<br>Number |

|--------------------------|---------------------------------------------------|--------------|----------------------------|

| TEMPDIODEp               | Positive pin of temperature diode in<br>Stratix V | -            | PIN_P6                     |

| TEMPDIODEn               | Negative pin of temperature diode<br>in Stratix V | -            | PIN_P7                     |

| FPGA_I2C_SCL             | SMBus clock                                       | 1.5-V        | PIN_AN11                   |

| FPGA_I2C_SDA        | SMBus data              | 1.5-V | PIN_AP9  |

|---------------------|-------------------------|-------|----------|

| TEMP_OVERT_n        | SMBus alert (interrupt) | 1.5-V | PIN_AR9  |

| TEMP_INT_n          | SMBus alert (interrupt) | 1.5-V | PIN_AT8  |

| POWER_MONITOR_ALERT | Active-high ALERT input | 1.5-V | PIN_AY9  |

| FAN_ALERT_n         | Active-low ALERT input  | 1.5-V | PIN_AM11 |

# **2.5 Clock Circuit**

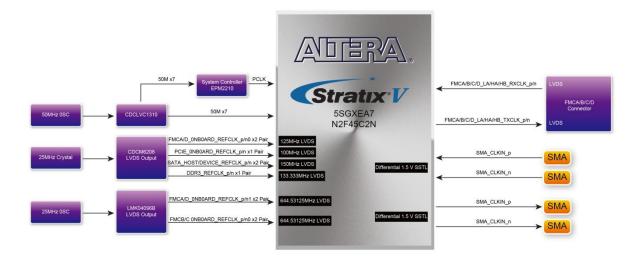

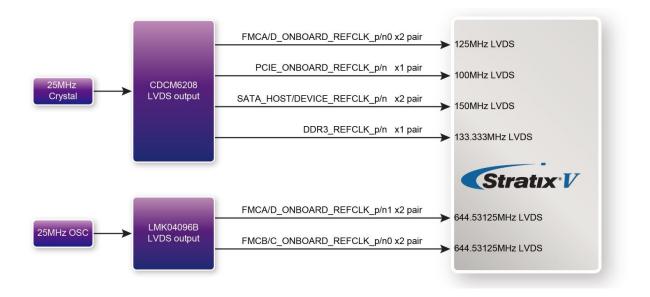

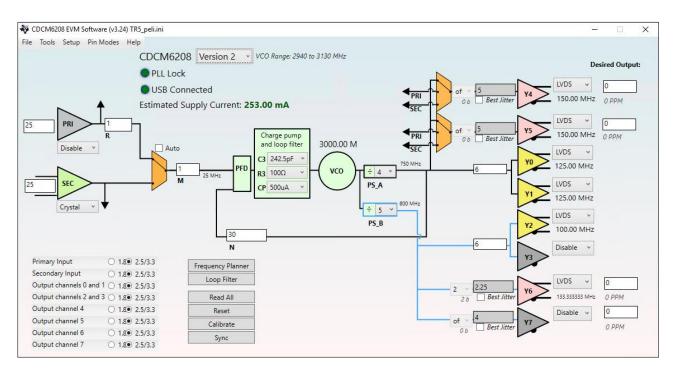

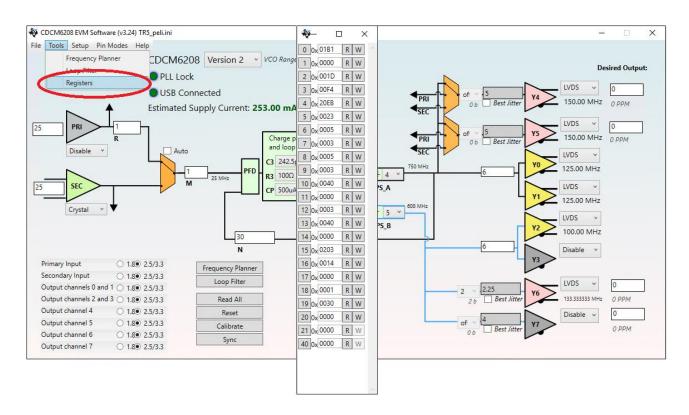

The development board includes one 50 MHz and two programmable clock generators. **Figure 2-11** shows the default frequencies of on-board all external clocks going to the Stratix V GX FPGA.

#### Figure 2-11 Clock circuit of the FPGA Board

A clock buffer is used to duplicate the 50 MHz oscillator, so there are seven 50MHz clocks fed into seven different FPGA banks. The two programming clock generators are low-jitter oscillators which are used to provide special and high quality clock signals for high-speed transceivers and high bandwidth memory. Through I2C serial interface, the clock generator controllers in the Stratix V GX FPGA can be used to program the CDCM6208 and LMK04096B to generate PCIe, SATA and high bandwidth memory reference clocks respectively. Two SMA connectors and Four FMC connectors provide external differential clock input(s) and clock output(s) respectively.

**Table 2-9** lists the clock source, signal names, default frequency and their corresponding Stratix V GX device pin numbers.

|        | -9 Clock Source, Signal Name |                  |                       | Stratix V |                                   |

|--------|------------------------------|------------------|-----------------------|-----------|-----------------------------------|

| Source | Schematic                    | Default          | I/O Standard          | GX Pin    | Application                       |

| 000100 | Signal Name                  | Frequency        |                       | Number    | Approviden                        |

|        | CLK_50_B3B                   |                  | 1.5-V                 | PIN_AW35  |                                   |

|        | CLK_50_B4A                   |                  | 1.5-V                 | PIN_AP10  |                                   |

| Y1     | CLK_50_B4D                   |                  | 1.2/1.5/1.8/2.5/3.0-V | PIN_AY18  |                                   |

|        | CLK_50_B7A                   | 50.0 MHz         | 1.2/1.5/1.8/2.5/3.0-V | PIN_M8    |                                   |

|        | CLK_50_B7D                   |                  | 1.2/1.5/1.8/2.5/3.0-V | PIN_J18   |                                   |

|        | CLK_50_B8A                   |                  | 1.2/1.5/1.8/2.5/3.0-V | PIN_R36   |                                   |

|        | CLK_50_B8D                   |                  | 1.2/1.5/1.8/2.5/3.0-V | PIN_R25   |                                   |

| J3     | SMA_CLKIN_p                  | User<br>Defined  | 1.5-V                 | PIN_BC8   | External Clock<br>Input           |

| J4     | SMA_CLKIN_n                  | User<br>Defined  | 1.5-V                 | PIN_BD8   | Clock Output                      |

| J1     | SMA_CLKOUT_p                 | User<br>Defined  | 1.5-V                 | PIN_AV8   |                                   |

| J2     | SMA_CLKOUT_n                 | User<br>Defined  | 1.5-V                 | PIN_AW9   |                                   |

|        | FMCA_ONBOARD_REFCLK_p0       | 125 MHz          | LVDS                  | PIN_Y38   | FMCA port xcvr<br>reference clock |

|        | FMCD_ONBOARD_REFCLK_p0       | 125 MHz          | LVDS                  | PIN_Y7    | FMCD port xcv<br>reference clock  |

| 1104   | PCIE_ONBOARD_REFCLK_p        | 100 MHz          | LVDS                  | PIN_AH39  | PCIe reference<br>clock           |

| U21    | SATA_DEVICE_REFCLK_p         | 150 MHz          | LVDS                  | PIN_AK7   | SATA Device<br>reference clock    |

|        | SATA_HOST_REFCLK_p           | 150 MHz          |                       | PIN_BB33  | SATA Host<br>reference clock      |

|        | DDR3_REFCLK_p                | 133.333<br>MHz   |                       |           | DDR3 reference<br>clock           |

|        | FMCA_ONBOARD_REFCLK_p1       | 644.53125<br>MHz | LVDS                  | PIN_T38   | FMCA port xcv<br>reference clock  |

|        | FMCD_ONBOARD_REFCLK_p1       | 644.53125<br>MHz | LVDS                  | PIN_T7    | FMCD port xcv<br>reference clock  |

| U43    | FMCC_ONBOARD_REFCLK_p0       | 644.53125<br>MHz | LVDS                  | PIN_AD39  | FMCB port xcv<br>reference clock  |

|        | FMCC_ONBOARD_REFCLK_p1       | 644.53125<br>MHz | LVDS                  | PIN_AD6   | FMCC port xcv<br>reference clock  |

| Table 2-9 Clock Source, | Signal Name.    | Default Frequency. | Pin Assianment | s and Functions |

|-------------------------|-----------------|--------------------|----------------|-----------------|

|                         | orginal Haillo, | Bolaalt Foquolioy, | , /            |                 |

Table 2-10 lists the programmable oscillator control pins, signal names, I/O standard and their

corresponding Stratix V GX device pin numbers.

| and Descriptions           |                          |              |                            |                                   |  |

|----------------------------|--------------------------|--------------|----------------------------|-----------------------------------|--|

| Programmable<br>Oscillator | Schematic<br>Signal Name | I/O Standard | Stratix V GX Pin<br>Number | Description                       |  |

| CDCM6208                   | CLOCK_SCL                | 2.5-V        | PIN_AR25                   | I2C bus, connected                |  |

| (U21)                      | CLOCK_SDA                | 2.5-V        | PIN_BC25                   | with CDCM6208                     |  |

|                            | LMK04906_CLK             | 2.5-V        | PIN_AT24                   | I2C bus master output             |  |

| LMK04906B<br>(U43)         | LMK04906_DATAIN          | 2.5-V        | PIN_BD25                   | only, connected with<br>LMK04096B |  |

|                            | LMK04906_DATAOUT         | 1.5-V        | PIN_BC29                   | I2C bus master input<br>signal    |  |

|                            | LMK04906_LE              | 1.5-V        | PIN_AT33                   | LMK04096B PLL<br>locked signal    |  |

# Table 2-10 Programmable oscillator control pin, Signal Name, I/O standard, Pin Assignments and Descriptions

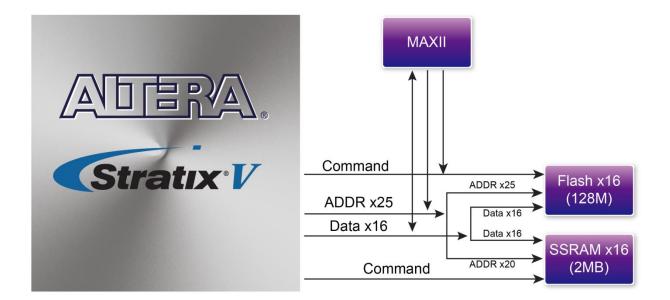

# **2.6 FLASH and SSRAM Memory**

The development board has a 1G bit CFI-compatible synchronous flash device for non-volatile storage of FPGA configuration data, user application data, and user code space, and a 2M byte ZBT SSRAM for data Cache.

The flash has a 16-bit data bus and allow for FPP x16 configuration. This device is part of the shared flash and MAX (FM) bus, which connects to the flash memory and MAX II CPLD (EPM2210) System Controller. The SSRAM also has a 16-bit data bus and share address and data bus with the flash. **Figure 2-12** shows the connections between the Flash, SSRAM, MAX and Stratix V GX FPGA.

#### Figure 2-12 Connection between the Flash, Max and Stratix V GX FPGA

Table 2-11 lists the flash pin assignments, signal names, and functions.

|                          | · · ·       | -            | •                          |

|--------------------------|-------------|--------------|----------------------------|

| Schematic<br>Signal Name | Description | I/O Standard | Stratix V GX<br>Pin Number |

| FSM_A1                   | Address bus | 2.5V         | PIN_AE11                   |

| FSM_A2                   | Address bus | 2.5V         | PIN_AD14                   |

| FSM_A3                   | Address bus | 2.5V         | PIN_AE14                   |

| FSM_A4                   | Address bus | 2.5V         | PIN_AE10                   |

| FSM_A5                   | Address bus | 2.5V         | PIN_AF10                   |

| FSM_A6                   | Address bus | 2.5V         | PIN_AE12                   |

| FSM_A7                   | Address bus | 2.5V         | PIN_AF11                   |

| FSM_A8                   | Address bus | 2.5V         | PIN_AG13                   |

| FSM_A9                   | Address bus | 2.5V         | PIN_AJ10                   |

| FSM_A10                  | Address bus | 2.5V         | PIN_AF13                   |

| FSM_A11                  | Address bus | 2.5V         | PIN_AE13                   |

| FSM_A12                  | Address bus | 2.5V         | PIN_AJ11                   |

| FSM_A13                  | Address bus | 2.5V         | PIN_BD11                   |

| FSM_A14                  | Address bus | 2.5V         | PIN_AW10                   |

| FSM_A15                  | Address bus | 2.5V         | PIN_AF14                   |

| FSM_A16                  | Address bus | 2.5V         | PIN_AY12                   |

| FSM_A17                  | Address bus | 2.5V         | PIN_AY10                   |

Table 2-13 Flash Memory Pin Assignments, Schematic Signal Names, and Functions

| FSM_A18         | Address bus                        | 2.5V | PIN_BD10 |

|-----------------|------------------------------------|------|----------|

| FSM_A19         | Address bus                        | 2.5V | PIN_BB12 |

| FSM_A20         | Address bus                        | 2.5V | PIN_BA12 |

| FSM_A21         | Address bus                        | 2.5V | PIN_BA10 |

| FSM_A22         | Address bus                        | 2.5V | PIN_BC11 |

| FSM_A23         | Address bus                        | 2.5V | PIN_AE9  |

| FSM_A24         | Address bus                        | 2.5V | PIN_AW11 |

| FSM_A25         | Address bus                        | 2.5V | PIN_BC10 |

| FSM_A26         | Address bus                        | 2.5V | PIN_BB11 |

| FSM_D0          | Data bus                           | 2.5V | PIN_AG10 |

| FSM_D1          | Data bus                           | 2.5V | PIN_AH10 |

| FSM_D2          | Data bus                           | 2.5V | PIN_AG11 |

| FSM_D3          | Data bus                           | 2.5V | PIN_AK12 |

| FSM_D4          | Data bus                           | 2.5V | PIN_AV10 |

| FSM_D5          | Data bus                           | 2.5V | PIN_AR12 |

| FSM_D6          | Data bus                           | 2.5V | PIN_AL12 |

| FSM_D7          | Data bus                           | 2.5V | PIN_AR13 |

| FSM_D8          | Data bus                           | 2.5V | PIN_AG9  |

| FSM_D9          | Data bus                           | 2.5V | PIN_AH12 |

| FSM_D10         | Data bus                           | 2.5V | PIN_AG12 |

| FSM_D11         | Data bus                           | 2.5V | PIN_AL11 |

| FSM_D12         | Data bus                           | 2.5V | PIN_AN12 |

| FSM_D13         | Data bus                           | 2.5V | PIN_AU9  |

| FSM_D14         | Data bus                           | 2.5V | PIN_AM13 |

| FSM_D15         | Data bus                           | 2.5V | PIN_AJ12 |

| FLASH_CLK       | Flash Clock                        | 2.5V | PIN_AU11 |

| FLASH_RESET_n   | Flash Reset, active low            | 2.5V | PIN_AV25 |

| FLASH_CE_n      | Flash Chip enable, active low      | 2.5V | PIN_AU24 |

| FLASH_OE_n      | Flash Output enable, active low    | 2.5V | PIN_AP12 |

| FLASH_WE_n      | Flash Write enable, active low     | 2.5V | PIN_AT12 |

| FLASH_ADV_n     | Flash Address valid, active<br>low | 2.5V | PIN_BD26 |

| FLASH_RDY_BSY_n | Flash ready output                 | 2.5V | PIN_AU25 |

| SSRAM_CLK       | SSRAM Clock                        | 2.5V | PIN_AP13 |

| SSRAM_CKE_n     | SSRAM Clock enable, active<br>low  | 2.5V | PIN_AW24 |

| SSRAM_CE_n      | SSRAM Chip enable, active<br>low   | 2.5V | PIN_AP24 |

| SSRAM_WE_n      | Flash Write enable, active low     | 2.5V | PIN_AV11 |

| SSRAM_OE_n      | Flash output enable, active low    | 2.5V | PIN_AU10 |

| SSRAM_ADV       | Flash Address valid, active<br>high | 2.5V | PIN_BC26 |

|-----------------|-------------------------------------|------|----------|

| SSRAM_BWA_n     | SSRAM Byte Write enable             | 2.5V | PIN_AY25 |

| SSRAM_BWB_n     | SSRAM Byte Write enable             | 2.5V | PIN_BA24 |

| FLASH_CLK       | Clock                               | 2.5V | PIN_T9   |

| FLASH_RESET_n   | Reset                               | 2.5V | PIN_C17  |

| FLASH_CE_n      | Chip enable of of flash-0           | 2.5V | PIN_H10  |

|                 | Chip enable of of flash-1           | 2.5V | PIN_N16  |

| FLASH_OE_n      | Output enable                       | 2.5V | PIN_C16  |

| FLASH_WE_n      | Write enable                        | 2.5V | PIN_U10  |

| FLASH_ADV_n     | Address valid                       | 2.5V | PIN_H7   |

| FLASH_RDY_BSY_n | Ready of flash-0                    | 2.5V | PIN_J8   |

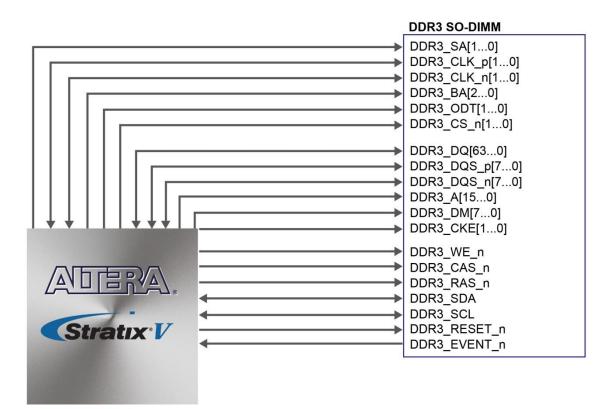

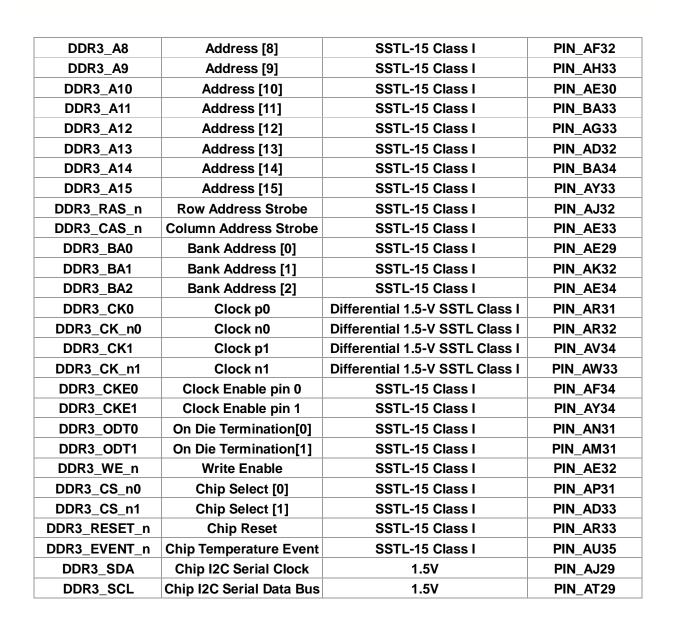

# 2.7 DDR3 SO-DIMM

The development board supports DDR3 SDRAM SO-DIMM. The DDR3 SODIMM socket is wired to support a maximum capacity of 8GB with a 64-bit data bus. Using differential DQS signaling for the DDR3 SDRAM interfaces, it is capable of running at up to 800MHz memory clock for a maximum theoretical bandwidth up to 95.4Gbps. **Figure 2-13** shows the connections between the DDR3 SDRAM SO-DIMMs and Stratix V GX FPGA.

Figure 2-13 Connection between the DDR3 and Stratix V GX FPGA

The pin assignments for DDR3 SDRAM SO-DIMM are listed in Table 2-14.

|                          | •           |                 |                            |  |

|--------------------------|-------------|-----------------|----------------------------|--|

| Schematic<br>Signal Name | Description | I/O Standard    | Stratix V GX Pin<br>Number |  |

| DDR3_DQ0                 | Data [0]    | SSTL-15 Class I | PIN_AH31                   |  |

| DDR3_DQ1                 | Data [1]    | SSTL-15 Class I | PIN_AJ31                   |  |

| DDR3_DQ2                 | Data [2]    | SSTL-15 Class I | PIN_AN30                   |  |

| DDR3_DQ3                 | Data [3]    | SSTL-15 Class I | PIN_AP30                   |  |

| DDR3_DQ4                 | Data [4]    | SSTL-15 Class I | PIN_AH30                   |  |

| DDR3_DQ5                 | Data [5]    | SSTL-15 Class I | PIN_AJ30                   |  |

| DDR3_DQ6                 | Data [6]    | SSTL-15 Class I | PIN_AR30                   |  |

| DDR3_DQ7                 | Data [7]    | SSTL-15 Class I | PIN_AT30                   |  |

| DDR3_DQ8                 | Data [8]    | SSTL-15 Class I | PIN_AM29                   |  |

| DDR3_DQ9                 | Data [9]    | SSTL-15 Class I | PIN_AN28                   |  |

| DDR3_DQ10                | Data [10]   | SSTL-15 Class I | PIN_AP28                   |  |

| DDR3_DQ11                | Data [11]   | SSTL-15 Class I | PIN_AR29                   |  |

Table 2-14 DDR3 Pin Assignments, Schematic Signal Names, and Functions

| DDR3_DQ12 | Data [12] | SSTL-15 Class I | PIN_AU31 |

|-----------|-----------|-----------------|----------|

| DDR3_DQ13 | Data [13] | SSTL-15 Class I | PIN_AV32 |

| DDR3_DQ14 | Data [14] | SSTL-15 Class I | PIN_AW32 |

| DDR3_DQ15 | Data [15] | SSTL-15 Class I | PIN_AV31 |

| DDR3_DQ16 | Data [16] | SSTL-15 Class I | PIN_AF28 |

| DDR3_DQ17 | Data [17] | SSTL-15 Class I | PIN_AF29 |

| DDR3_DQ18 | Data [18] | SSTL-15 Class I | PIN_AG30 |

| DDR3_DQ19 | Data [19] | SSTL-15 Class I | PIN_AG29 |

| DDR3_DQ20 | Data [20] | SSTL-15 Class I | PIN_AG28 |

| DDR3_DQ21 | Data [21] | SSTL-15 Class I | PIN_AG27 |

| DDR3_DQ22 | Data [22] | SSTL-15 Class I | PIN_AG26 |

| DDR3_DQ23 | Data [23] | SSTL-15 Class I | PIN_AG25 |

| DDR3_DQ24 | Data [24] | SSTL-15 Class I | PIN_BC31 |

| DDR3_DQ25 | Data [25] | SSTL-15 Class I | PIN_BC32 |

| DDR3_DQ26 | Data [26] | SSTL-15 Class I | PIN_BB30 |

| DDR3_DQ27 | Data [27] | SSTL-15 Class I | PIN_BD31 |

| DDR3_DQ28 | Data [28] | SSTL-15 Class I | PIN_BD32 |

| DDR3_DQ29 | Data [29] | SSTL-15 Class I | PIN_BA30 |

| DDR3_DQ30 | Data [30] | SSTL-15 Class I | PIN_AY31 |

| DDR3_DQ31 | Data [31] | SSTL-15 Class I | PIN_AW30 |

| DDR3_DQ32 | Data [32] | SSTL-15 Class I | PIN_BB29 |

| DDR3_DQ33 | Data [33] | SSTL-15 Class I | PIN_BB27 |

| DDR3_DQ34 | Data [34] | SSTL-15 Class I | PIN_BA27 |

| DDR3_DQ35 | Data [35] | SSTL-15 Class I | PIN_AW27 |

| DDR3_DQ36 | Data [36] | SSTL-15 Class I | PIN_AY28 |

| DDR3_DQ37 | Data [37] | SSTL-15 Class I | PIN_BA28 |

| DDR3_DQ38 | Data [38] | SSTL-15 Class I | PIN_AW29 |

| DDR3_DQ39 | Data [39] | SSTL-15 Class I | PIN_AY27 |

| DDR3_DQ40 | Data [40] | SSTL-15 Class I | PIN_AT27 |

| DDR3_DQ41 | Data [41] | SSTL-15 Class I | PIN_AN25 |

| DDR3_DQ42 | Data [42] | SSTL-15 Class I | PIN_AM25 |

| DDR3_DQ43 | Data [43] | SSTL-15 Class I | PIN_AL25 |

| DDR3_DQ44 | Data [44] | SSTL-15 Class I | PIN_AW26 |

| DDR3_DQ45 | Data [45] | SSTL-15 Class I | PIN_AV26 |

| DDR3_DQ46 | Data [46] | SSTL-15 Class I | PIN_AU27 |

| DDR3_DQ47 | Data [47] | SSTL-15 Class I | PIN_AM26 |

| DDR3_DQ48 | Data [48] | SSTL-15 Class I | PIN_AU28 |

| DDR3_DQ49 | Data [49] | SSTL-15 Class I | PIN_AU29 |

| DDR3_DQ50 | Data [50] | SSTL-15 Class I | PIN_AM28 |

| DDR3_DQ51 | Data [51] | SSTL-15 Class I | PIN_AL27 |

| DDR3_DQ52 | Data [52] | SSTL-15 Class I | PIN_AV28 |

| DDR3 DQ53 | Data [53] | SSTL-15 Class I | PIN_AV29 |

| DDR3_DQ54   | Data [54]        | SSTL-15 Class I                 | PIN_AL28 |

|-------------|------------------|---------------------------------|----------|

| DDR3_DQ55   | Data [55]        | SSTL-15 Class I                 | PIN_AK27 |

| DDR3_DQ56   | Data [56]        | SSTL-15 Class I                 | PIN_AK24 |

| DDR3_DQ57   | Data [57]        | SSTL-15 Class I                 | PIN_AJ24 |

| DDR3_DQ58   | Data [58]        | SSTL-15 Class I                 | PIN_AH24 |

| DDR3_DQ59   | Data [59]        | SSTL-15 Class I                 | PIN_AH25 |

| DDR3_DQ60   | Data [60]        | SSTL-15 Class I                 | PIN_AH28 |

| DDR3_DQ61   | Data [61]        | SSTL-15 Class I                 | PIN_AJ28 |

| DDR3_DQ62   | Data [62]        | SSTL-15 Class I                 | PIN_AL26 |

| DDR3_DQ63   | Data [63]        | SSTL-15 Class I                 | PIN_AK26 |

| DDR3_DQS0   | Data Strobe p[0] | Differential 1.5-V SSTL Class I | PIN_AL30 |

| DDR3_DQS_n0 | Data Strobe n[0] | Differential 1.5-V SSTL Class I | PIN_AL31 |

| DDR3_DQS1   | Data Strobe p[1] | Differential 1.5-V SSTL Class I | PIN_AK30 |

| DDR3_DQS_n1 | Data Strobe n[1] | Differential 1.5-V SSTL Class I | PIN_AL29 |

| DDR3_DQS2   | Data Strobe p[2] | Differential 1.5-V SSTL Class I | PIN_AE27 |

| DDR3_DQS_n2 | Data Strobe n[2] | Differential 1.5-V SSTL Class I | PIN_AE28 |

| DDR3_DQS3   | Data Strobe p[3] | Differential 1.5-V SSTL Class I | PIN_AY30 |

| DDR3_DQS_n3 | Data Strobe n[4] | Differential 1.5-V SSTL Class I | PIN_BA29 |

| DDR3_DQS4   | Data Strobe p[4] | Differential 1.5-V SSTL Class I | PIN_BC28 |

| DDR3_DQS_n4 | Data Strobe n[4] | Differential 1.5-V SSTL Class I | PIN_BD28 |

| DDR3_DQS5   | Data Strobe p[5] | Differential 1.5-V SSTL Class I | PIN_AT26 |

| DDR3_DQS_n5 | Data Strobe n[5] | Differential 1.5-V SSTL Class I | PIN_AU26 |

| DDR3_DQS6   | Data Strobe p[6] | Differential 1.5-V SSTL Class I | PIN_AR27 |

| DDR3_DQS_n6 | Data Strobe n[6] | Differential 1.5-V SSTL Class I | PIN_AR28 |

| DDR3_DQS7   | Data Strobe p[7] | Differential 1.5-V SSTL Class I | PIN_AJ25 |

| DDR3_DQS_n7 | Data Strobe n[7] | Differential 1.5-V SSTL Class I | PIN_AJ26 |

| DDR3_DM0    | Data Mask [0]    | SSTL-15 Class I                 | PIN_AU32 |

| DDR3_DM1    | Data Mask [1]    | SSTL-15 Class I                 | PIN_AU30 |

| DDR3_DM2    | Data Mask [2]    | SSTL-15 Class I                 | PIN_AK29 |

| DDR3_DM3    | Data Mask [3]    | SSTL-15 Class I                 | PIN_BB32 |

| DDR3_DM4    | Data Mask [4]    | SSTL-15 Class I                 | PIN_BD29 |

| DDR3_DM5    | Data Mask [5]    | SSTL-15 Class I                 | PIN_AR26 |

| DDR3_DM6    | Data Mask [6]    | SSTL-15 Class I                 | PIN_AP27 |

| DDR3_DM7    | Data Mask [7]    | SSTL-15 Class I                 | PIN_AJ27 |

| DDR3_A0     | Address [0]      | SSTL-15 Class I                 | PIN_AM32 |

| DDR3_A1     | Address [1]      | SSTL-15 Class I                 | PIN_AF31 |

| DDR3_A2     | Address [2]      | SSTL-15 Class I                 | PIN_AJ33 |

| DDR3_A3     | Address [3]      | SSTL-15 Class I                 | PIN_AE31 |

| DDR3_A4     | Address [4]      | SSTL-15 Class I                 | PIN_AP33 |

| DDR3_A5     | Address [5]      | SSTL-15 Class I                 | PIN_AG32 |

| DDR3_A6     | Address [6]      | SSTL-15 Class I                 | PIN_AN33 |

| DDR3_A7     | Address [7]      | SSTL-15 Class I                 | PIN_AK33 |

# **2.8 FMC Connectors**

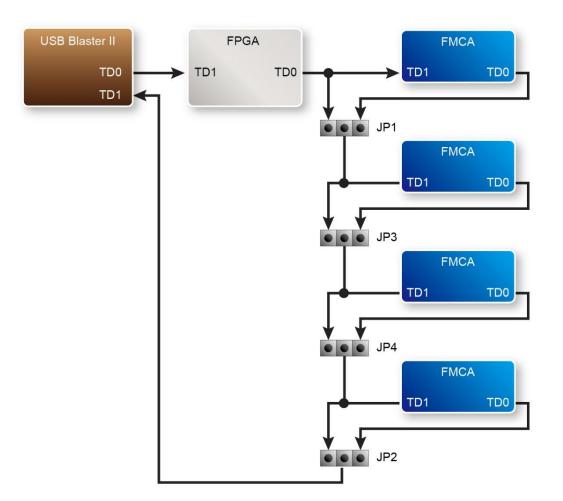

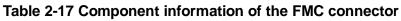

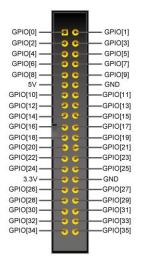

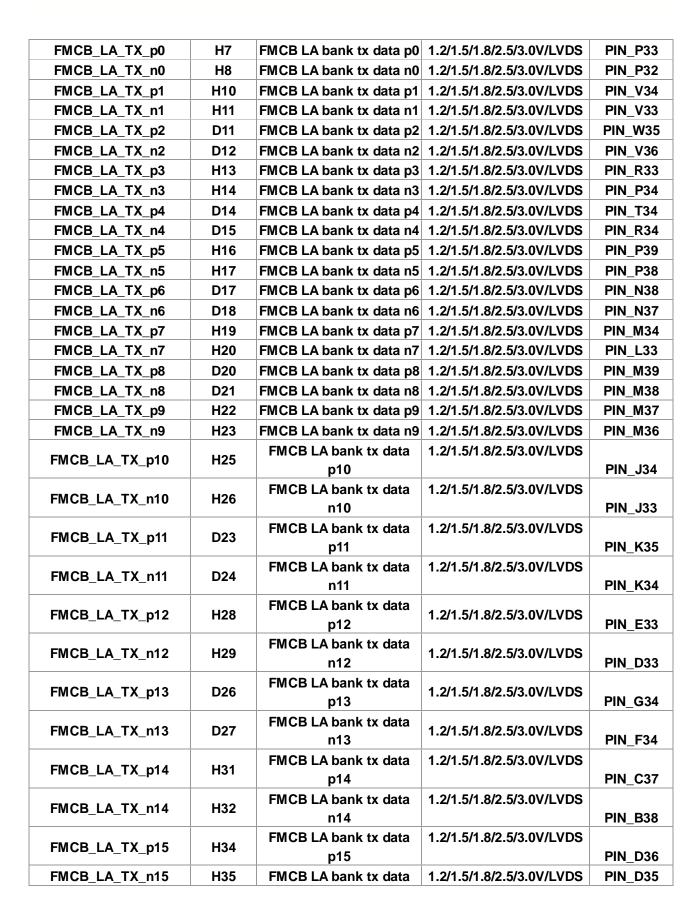

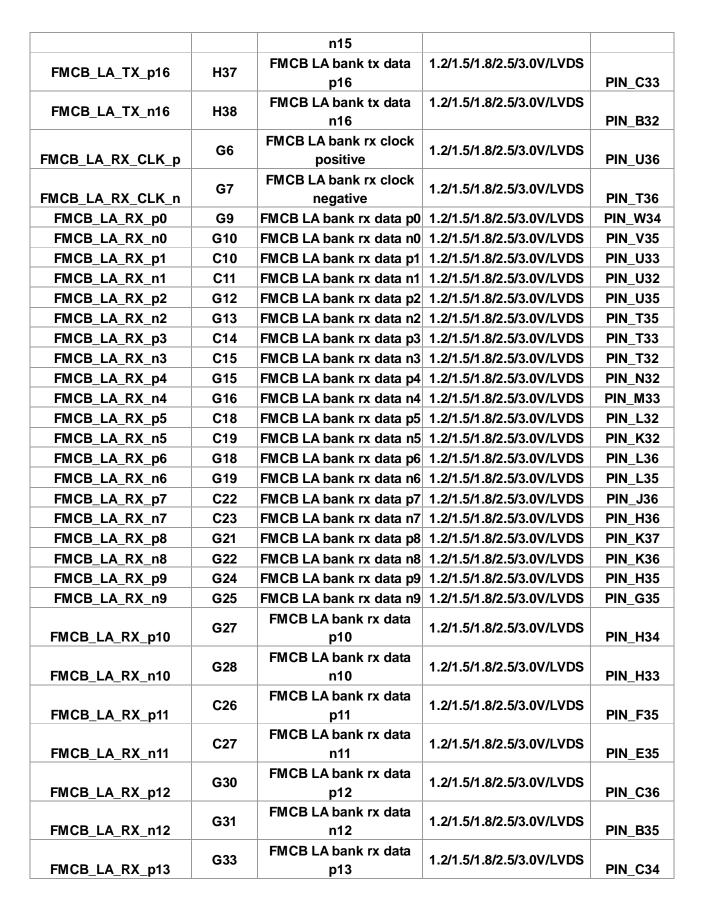

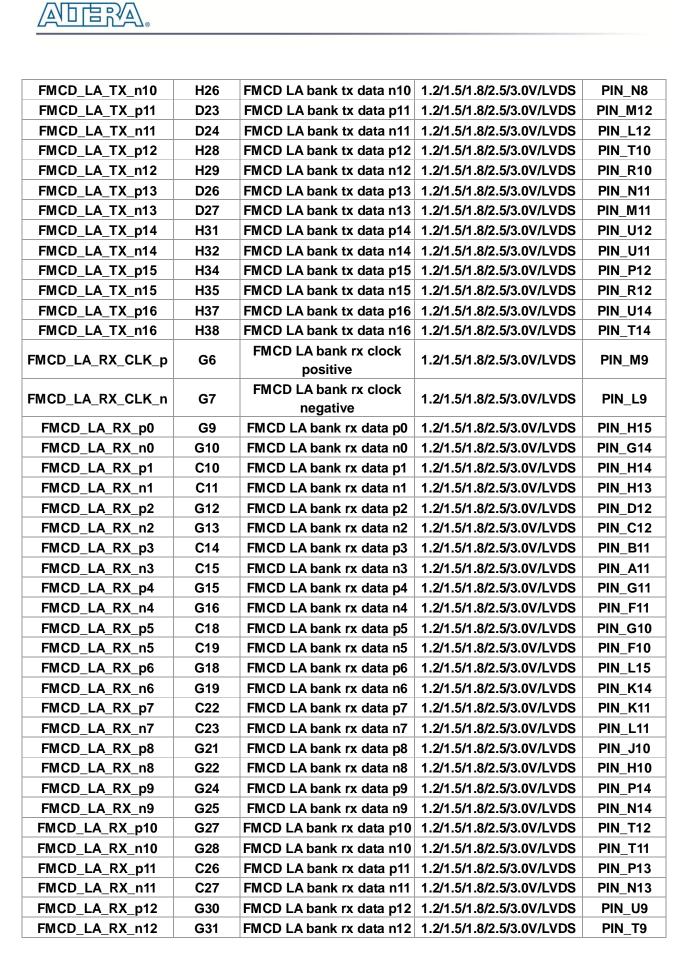

The FPGA Mezzanine Card (FMC) interface provides a mechanism to extend the peripheral-set of an FPGA host board by means of add-on daughter cards, which can address today's high speed signaling requirements as well as low-speed device interface support. The FMC interfaces support JTAG, clock outputs and inputs, high-speed serial I/O (transceivers), and single-ended or differential signaling. The detailed specifications of the FMC connectors are described below:

#### ■ 4 FMC Connector

][= ₽∜▲

There are four FMC connectors on the TR5 board are: FMCA, FMCB, FMCC, FMCD. Both FMCA and FMCD are High Pin Count (HPC) size of connectors and FMCB and FMCC are Low Pin Count (LPC) size of connectors (See **Figure 2-13**). The HPC connector on TR5 board can provides 172 user-define, single-ended signals (include clock signals) and 10 serial transceiver pairs (See **Figure 2-15**). The LPC connector can provides 76 user-define, single-ended signals (include clock signals) and 1 serial transceiver pairs (See **Figure 2-16**). The HPC and LPC connectors use the same mechanical connector. The only difference is which signals are actually populated. Thus, cards with LPC connectors can be plugged into HPC sites. Please note that some standard FMC cards may not work with TR5 due to unidirectional LVDS due to Stratix V device.

| 1<br>2<br>3 | FMC_X_VREF | GND      |             |             |             |             |               |             |               |           |

|-------------|------------|----------|-------------|-------------|-------------|-------------|---------------|-------------|---------------|-----------|

| 3           |            | GND      | FMC_X_VREF  | GND         | PG_M2C      | GND         | PG_C2M        | GND         | NC            | GND       |

| -           | GND        | HA_TX_p5 | NC          | CLK_M2C_p1  | GND         | HA01_P_CC   | GND           | DP_C2M_p0   | GND           | DP_M2C_p1 |

|             | GND        | HA_TX_p5 | GND         | CLK_M2C_n1  | GND         | HA01_N_CC   | GND           | DP_C2M_n0   | GND           | DP_M2C_n1 |

| 4           | HA_TX_p8   | GND      | CLK_M2C_p0  | GND         | HA00_P_CC   | GND         | GBTCLK_M2C_p0 | GND         | DP_M2C_p9     | GND       |

| 5           | HA_TX_n8   | GND      | CLK_M2C_n0  | GND         | HA00_N_CC   | GND         | GBTCLK_M2C_n0 | GND         | DP_M2C_n9     | GND       |

| 6           | GND        | HA_RX_p5 | GND         | LA_RX_CLK_p | GND         | HA_RX_p0    | GND           | DP_M2C_p0   | GND           | DP_M2C_p2 |

| 7           | HA_RX_p8   | HA_RX_n5 | LA_TX_p0    | LA_RX_CLK_n | HA_TX_p0    | HA_RX_n0    | GND           | DP_M2C_n0   | GND           | DP_M2C_n2 |

| 8           | HA_RX_n8   | GND      | LA_TX_n0    | GND         | HA_TX_n0    | GND         | LA_TX_CLK_p   | GND         | DP_M2C_p8     | GND       |

| 9           | GND        | HA_TX_p6 | GND         | LA_RX_p0    | GND         | HA_RX_p1    | LA_TX_CLK_n   | GND         | DP_M2C_n8     | GND       |

| 10          | HA_TX_p9   | HA_TX_n6 | LA_TX_p1    | LA_RX_n0    | HA_TX_p1    | HA_RX_n1    | GND           | LA_RX_p1    | GND           | DP_M2C_p3 |

| 11          | HA_TX_n9   | GND      | LA_TX_n1    | GND         | HA_TX_n1    | GND         | LA_TX_p2      | LA_RX_n1    | GND           | DP_M2C_n3 |

| 12          | GND        | HA_RX_p6 | GND         | LA_RX_p2    | GND         | HA_RX_p2    | LA_TX_n2      | GND         | DP_M2C_p7     | GND       |

| 13          | HA_RX_p9   | HA_RX_n6 | LA_TX_p3    | LA_RX_n2    | HA_TX_p2    | HA_RX_n2    | GND           | GND         | DP_M2C_n7     | GND       |

| 14          | HA_RX_n9   | GND      | LA_TX_n3    | GND         | HA_TX_n2    | GND         | LA_TX_p4      | LA_RX_p3    | GND           | DP_M2C_p4 |

| 15          | GND        | HA_TX_p7 | GND         | LA_RX_p4    | GND         | HA_RX_p3    | LA_TX_n4      | LA_RX_n3    | GND           | DP_M2C_n4 |

| 16          | HA_TX_p10  | HA_TX_n7 | LA_TX_p5    | LA_RX_n4    | HA_TX_p3    | HA_RX_n3    | GND           | GND         | DP_M2C_p6     | GND       |

| 17          | HA_TX_n10  | GND      | LA_TX_n5    | GND         | HA_TX_n3    | GND         | LA_TX_p6      | GND         | DP_M2C_n6     | GND       |

| 18          | GND        | HA_RX_p7 | GND         | LA_RX_p6    | GND         | HA_RX_p4    | LA_TX_n6      | LA_RX_p5    | GND           | DP_M2C_p5 |

| 19          | HA_RX_p10  | HA_RX_n7 | LA_TX_p7    | LA_RX_n6    | HA_TX_p4    | HA_RX_n4    | GND           | LA_RX_n5    | GND           | DP_M2C_n5 |

| 20          | HA_RX_n10  | GND      | LA_TX_n7    | GND         | HA_TX_n4    | GND         | LA_TX_p8      | GND         | GBTCLK_M2C_p1 | GND       |

| 21          | GND        | HB_RX_p5 | GND         | LA_RX_p8    | GND         | HB_RX_p0    | LA_TX_n8      | GND         | GBTCLK_M2C_n1 | GND       |

| 22          | HA_RX_p8   | HB_RX_n5 | LA_TX_p9    | LA_RX_n8    | HB_TX_p0    | HB_RX_n0    | GND           | LA_RX_p7    | GND           | DP_C2M_p1 |

| 23          | HA_RX_n8   | GND      | LA_TX_n9    | GND         | HB_TX_n0    | GND         | LA_TX_p11     | LA_RX_n7    | GND           | DP_C2M_n1 |

| 24          | GND        | HB_TX_p5 | GND         | LA_RX_p9    | GND         | HB_RX_p1    | LA_TX_n11     | GND         | DP_C2M_p9     | GND       |

| 25          | HB_TX_p8   | HB_TX_n5 | LA_TX_p10   | LA_RX_n9    | HB_TX_p1    | HB_RX_n1    | GND           | GND         | DP_C2M_n9     | GND       |

| 26          | HB_TX_n8   | GND      | LA_TX_n10   | GND         | HB_TX_n1    | GND         | LA_TX_p13     | LA_RX_p11   | GND           | DP_C2M_p2 |

| 27          | GND        | HB_RX_p6 | GND         | LA_RX_p10   | GND         | HB_RX_p2    | LA_TX_n13     | LA_RX_n11   | GND           | DP_C2M_n2 |

| 28          | HB_RX_p9   | HB_RX_n6 | LA_TX_p12   | LA_RX_n10   | HB_TX_p2    | HB_RX_n2    | GND           | GND         | DP_C2M_p8     | GND       |

| 29          | HB_RX_n9   | GND      | LA_TX_n12   | GND         | HB_TX_n2    | GND         | тск           | GND         | DP_C2M_n8     | GND       |

| 30          | GND        | HB_TX_p6 | GND         | LA_RX_p12   | GND         | HB_RX_p3    | TDI           | SCL         | GND           | DP_C2M_p3 |

| 31          | HB_TX_p9   | HB_TX_n6 | LA_TX_p14   | LA_RX_n12   | HB_TX_p3    | HB_RX_n3    | TDO           | SDA         | GND           | DP_C2M_n3 |

| 32          | HB_TX_n9   | GND      | LA_TX_n14   | GND         | HB_TX_n3    | GND         | VCC3P3        | GND         | DP_C2M_p7     | GND       |

| 33          | GND        | HB_TX_p7 | GND         | LA_RX_p13   | GND         | HB_RX_p4    | TMS           | GND         | DP_C2M_n7     | GND       |

| 34          | HB_RX_p10  | HB_TX_n7 | LA_TX_p15   | LA_RX_n13   | HB_TX_p4    | HB_RX_n4    | TRST_L        | GA0         | GND           | DP_C2M_p4 |

| 35          | HB_RX_n10  | GND      | LA_TX_n15   | GND         | HB_TX_n4    | GND         | GA1           | VCC12_FMC_X | GND           | DP_C2M_n4 |

| 36          | GND        | HB_TX_p7 | GND         | LA_RX_p14   | GND         | HB_RX_CLK_p | VCC3P3        | GND         | DP_C2M_p6     | GND       |

| 37          | HB_TX_p10  | HB_TX_n7 | LA_TX_p16   | LA_RX_n14   | HB_TX_CLK_p | HB_RX_CLK_n | GND           | VCC12_FMC_X | DP_C2M_n6     | GND       |

| 38          | HB_TX_n10  | GND      | LA_TX_n16   | GND         | HB_TX_CLK_n | GND         | VCC3P3        | GND         | GND           | DP_C2M_p5 |

| 39          | GND        | NC       | GND         | VCCIO_FMC_X | GND         | VCCIO_FMC_X | GND           | VCC3P3      | GND           | DP_C2M_n5 |

| 40          | NC         | GND      | VCCIO_FMC_X | GND         | VCCIO_FMC_X | GND         | VCC3P3        | GND         | NC            | GND       |

Figure 2-15 Pin-Out of the high pin count FMC connector

| 1           2           3           4           5           6           7           8           9           10           11           12           13           14           15           16           17           18           20           21 | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>N | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>N | FMC_X_VREF           NC           GND           CLK_M2C_00           GND           LA_TX_00           GND           LA_TX_n0           GND           LA_TX_n1           GND           LA_TX_n2 | GND<br>CLK_M2C_p1<br>CLK_M2C_n1<br>GND<br>LA_RX_CLK_p<br>LA_RX_CLK_n<br>GND<br>LA_RX_p0<br>LA_RX_p0<br>GND<br>LA_RX_p2 | XC<br>XC<br>XC<br>XC<br>XC<br>XC<br>XC<br>XC<br>XC<br>XC<br>XC<br>XC<br>XC<br>X | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC | PG_C2M           GND           GND           GBTCLK_M2C_P0           GBTCLK_M2C_N0           GND           GND           GND           LA_TX_CLK_P           LA_TX_CLK_n | GND<br>DP_C2M_p0<br>DP_C2M_n0<br>GND<br>DP_M2C_p0<br>DP_M2C_n0<br>GND<br>GND | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| 3           4           5           6           7           8           9           10           11           12           13           13           14           15           16           17           18           19           20            | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>N | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC            | GND<br>CLK_M2C_p0<br>CLK_M2C_n0<br>GND<br>LA_TX_n0<br>LA_TX_n0<br>GND<br>LA_TX_p1<br>LA_TX_p1<br>LA_TX_n1<br>GND<br>LA_TX_p3                                                                   | CLK_M2C_n1<br>GND<br>LA_RX_CLK_p<br>LA_RX_CLK_n<br>GND<br>LA_RX_p0<br>LA_RX_n0<br>GND<br>LA_RX_p2                      | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                              | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC             | GND<br>GBTCLK_M2C_p0<br>GBTCLK_M2C_n0<br>GND<br>GND<br>LA_TX_CLK_p<br>LA_TX_CLK_n                                                                                        | DP_C2M_n0<br>GND<br>DP_M2C_p0<br>DP_M2C_n0<br>GND                            | NC<br>NC<br>NC<br>NC<br>NC<br>NC                   | NC<br>NC<br>NC<br>NC<br>NC<br>NC                   |

| 4         5           6         7           7         8           9         9           10         11           12         13           14         15           16         17           18         19           20         19                    | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>N | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                        | CLK_M2C_p0<br>CLK_M2C_n0<br>GND<br>LA_TX_p0<br>LA_TX_n0<br>GND<br>LA_TX_p1<br>LA_TX_p1<br>LA_TX_p1<br>LA_TX_p3                                                                                 | GND<br>GND<br>LA_RX_CLK_p<br>LA_RX_CLK_n<br>GND<br>LA_RX_p0<br>LA_RX_n0<br>GND<br>LA_RX_p2                             | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                                    | NC<br>NC<br>NC<br>NC<br>NC<br>NC                   | GBTCLK_M2C_p0       GBTCLK_M2C_n0       GND       GND       LA_TX_CLK_p       LA_TX_CLK_n                                                                                | GND<br>GND<br>DP_M2C_p0<br>DP_M2C_n0<br>GND                                  | NC<br>NC<br>NC<br>NC<br>NC                         | NC<br>NC<br>NC<br>NC<br>NC                         |

| 5         6           7         8           9         10           11         12           13         14           15         16           17         18           19         20                                                                 | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>N | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                        | CLK_M2C_n0<br>GND<br>LA_TX_p0<br>LA_TX_n0<br>GND<br>LA_TX_p1<br>LA_TX_p1<br>LA_TX_p3                                                                                                           | GND<br>LA_RX_CLK_p<br>LA_RX_CLK_n<br>GND<br>LA_RX_p0<br>LA_RX_n0<br>GND<br>LA_RX_p2                                    | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                                          | NC<br>NC<br>NC<br>NC<br>NC                         | GBTCLK_M2C_n0<br>GND<br>GND<br>LA_TX_CLK_p<br>LA_TX_CLK_n                                                                                                                | GND<br>DP_M2C_p0<br>DP_M2C_n0<br>GND                                         | NC<br>NC<br>NC<br>NC                               | NC<br>NC<br>NC<br>NC                               |

| 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20                                                                                                                                                               | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                  | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                                    | GND<br>LA_TX_p0<br>LA_TX_n0<br>GND<br>LA_TX_p1<br>LA_TX_n1<br>GND<br>LA_TX_p3                                                                                                                  | LA_RX_CLK_p<br>LA_RX_CLK_n<br>GND<br>LA_RX_p0<br>LA_RX_n0<br>GND<br>LA_RX_p2                                           | NC<br>NC<br>NC<br>NC<br>NC                                                      | NC<br>NC<br>NC<br>NC                               | GND<br>GND<br>LA_TX_CLK_p<br>LA_TX_CLK_n                                                                                                                                 | DP_M2C_p0<br>DP_M2C_n0<br>GND                                                | NC<br>NC<br>NC                                     | NC<br>NC<br>NC                                     |

| 7         8           9         10           11         12           13         14           15         16           16         17           18         19           20         20                                                               | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                        | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                                    | LA_TX_p0<br>LA_TX_n0<br>GND<br>LA_TX_p1<br>LA_TX_n1<br>GND<br>LA_TX_p3                                                                                                                         | LA_RX_CLK_n<br>GND<br>LA_RX_p0<br>LA_RX_n0<br>GND<br>LA_RX_p2                                                          | NC<br>NC<br>NC<br>NC                                                            | NC<br>NC<br>NC                                     | GND<br>LA_TX_CLK_p<br>LA_TX_CLK_n                                                                                                                                        | DP_M2C_n0<br>GND                                                             | NC<br>NC                                           | NC<br>NC                                           |

| 8         9           9         10           11         12           13         14           15         16           17         18           19         20                                                                                       | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                  | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                                          | LA_TX_n0<br>GND<br>LA_TX_p1<br>LA_TX_n1<br>GND<br>LA_TX_p3                                                                                                                                     | GND<br>LA_RX_p0<br>LA_RX_n0<br>GND<br>LA_RX_p2                                                                         | NC<br>NC<br>NC                                                                  | NC<br>NC                                           | LA_TX_CLK_p<br>LA_TX_CLK_n                                                                                                                                               | GND                                                                          | NC                                                 | NC                                                 |

| 9       10       11       12       13       14       15       16       17       18       19       20                                                                                                                                             | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                              | NC<br>NC<br>NC<br>NC<br>NC<br>NC                                                | GND<br>LA_TX_p1<br>LA_TX_n1<br>GND<br>LA_TX_p3                                                                                                                                                 | LA_RX_p0<br>LA_RX_n0<br>GND<br>LA_RX_p2                                                                                | NC<br>NC                                                                        | NC                                                 | LA_TX_CLK_n                                                                                                                                                              |                                                                              |                                                    |                                                    |

| 10       11       12       13       14       15       16       17       18       19       20                                                                                                                                                     | NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC                                          | NC<br>NC<br>NC<br>NC<br>NC                                                      | LA_TX_p1<br>LA_TX_n1<br>GND<br>LA_TX_p3                                                                                                                                                        | LA_RX_n0<br>GND<br>LA_RX_p2                                                                                            | NC                                                                              |                                                    |                                                                                                                                                                          | GND                                                                          | NC                                                 | NC                                                 |

| 11       12       13       14       15       16       17       18       19       20                                                                                                                                                              | NC<br>NC<br>NC<br>NC<br>NC<br>NC                                                | NC<br>NC<br>NC<br>NC                                                            | LA_TX_n1<br>GND<br>LA_TX_p3                                                                                                                                                                    | GND<br>LA_RX_p2                                                                                                        |                                                                                 | NC                                                 |                                                                                                                                                                          |                                                                              |                                                    |                                                    |

| 12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20                                                                                                                                                                                               | NC<br>NC<br>NC<br>NC<br>NC                                                      | NC<br>NC<br>NC                                                                  | GND<br>LA_TX_p3                                                                                                                                                                                | LA_RX_p2                                                                                                               | NC                                                                              |                                                    | GND                                                                                                                                                                      | LA_RX_p1                                                                     | NC                                                 | NC                                                 |

| 13       14       15       16       17       18       19       20                                                                                                                                                                                | NC<br>NC<br>NC<br>NC                                                            | NC<br>NC                                                                        | LA_TX_p3                                                                                                                                                                                       |                                                                                                                        |                                                                                 | NC                                                 | LA_TX_p2                                                                                                                                                                 | LA_RX_n1                                                                     | NC                                                 | NC                                                 |

| 14       15       16       17       18       19       20                                                                                                                                                                                         | NC<br>NC<br>NC                                                                  | NC                                                                              |                                                                                                                                                                                                |                                                                                                                        | NC                                                                              | NC                                                 | LA_TX_n2                                                                                                                                                                 | GND                                                                          | NC                                                 | NC                                                 |

| 15<br>16<br>17<br>18<br>19<br>20                                                                                                                                                                                                                 | NC<br>NC                                                                        |                                                                                 |                                                                                                                                                                                                | LA_RX_n2                                                                                                               | NC                                                                              | NC                                                 | GND                                                                                                                                                                      | GND                                                                          | NC                                                 | NC                                                 |

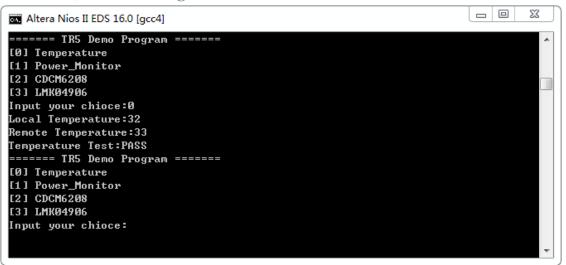

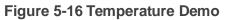

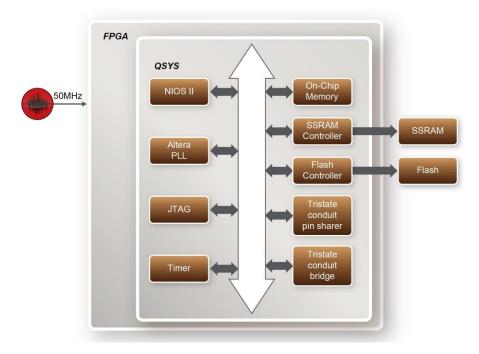

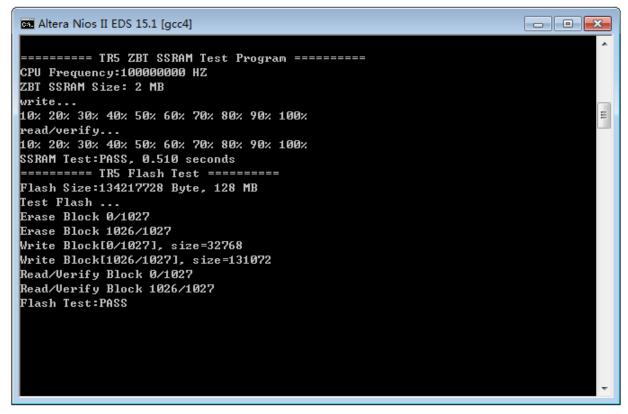

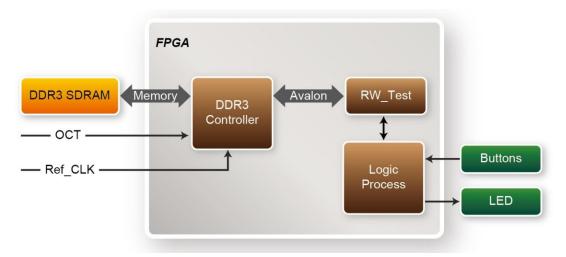

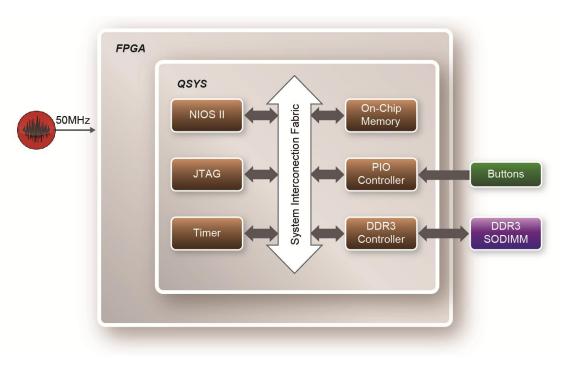

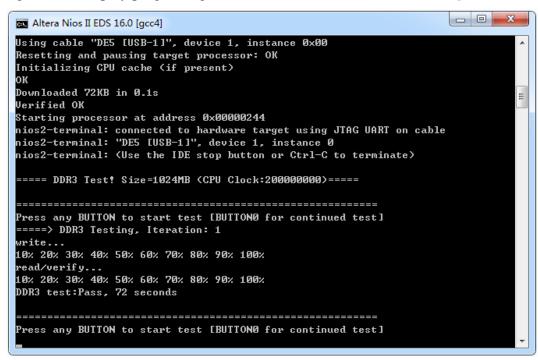

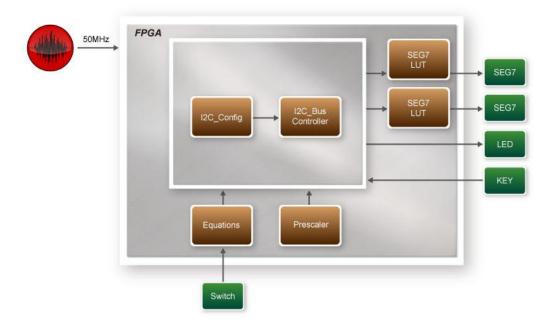

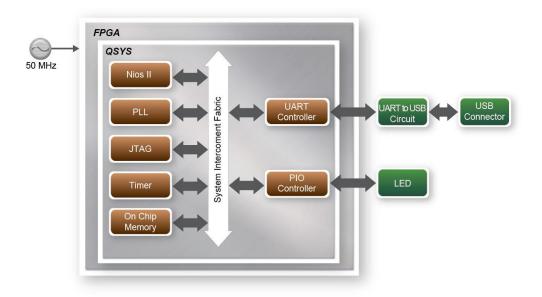

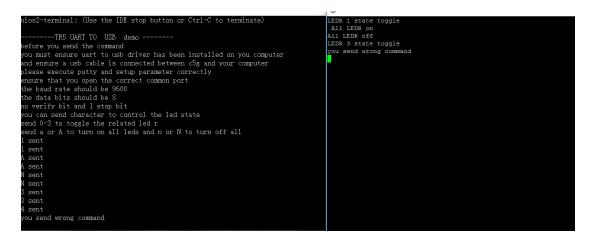

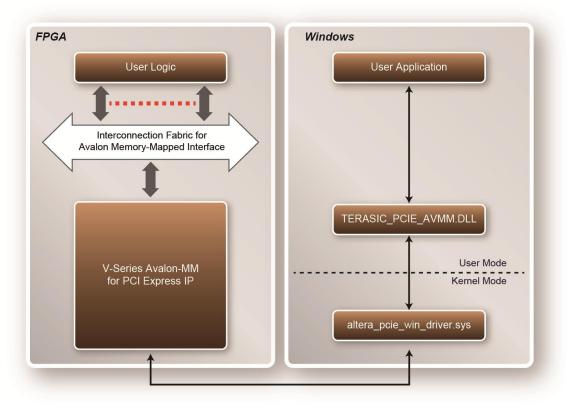

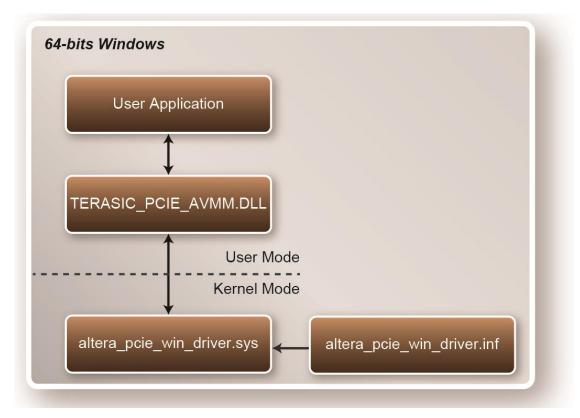

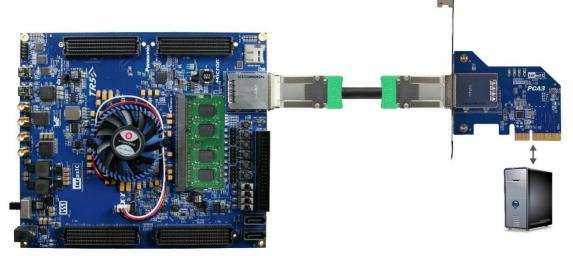

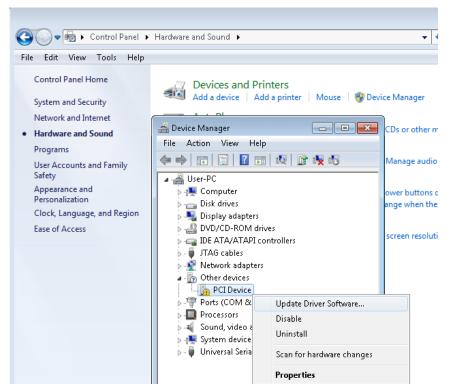

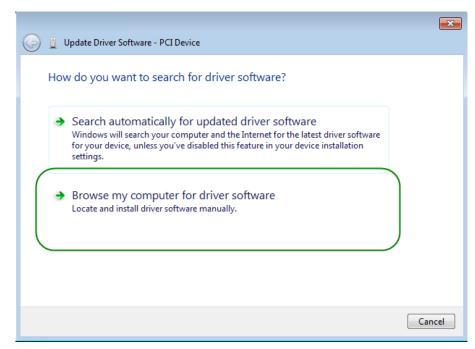

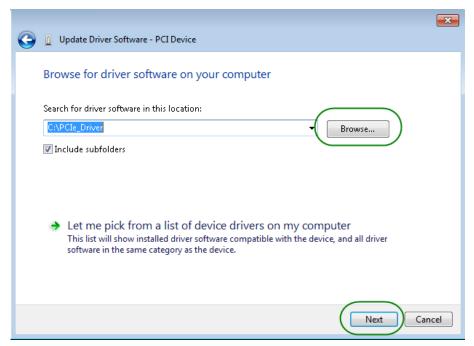

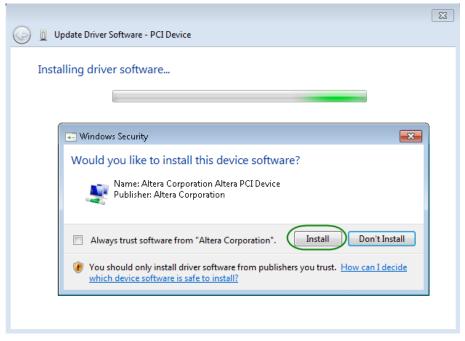

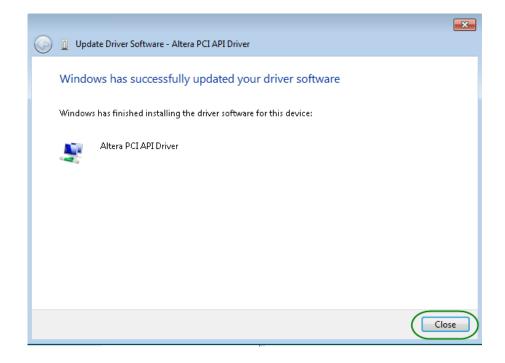

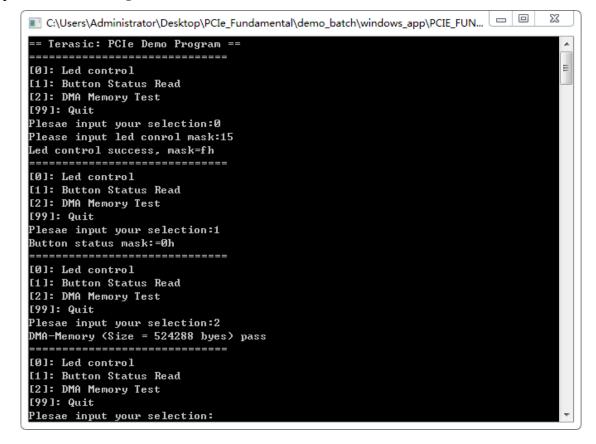

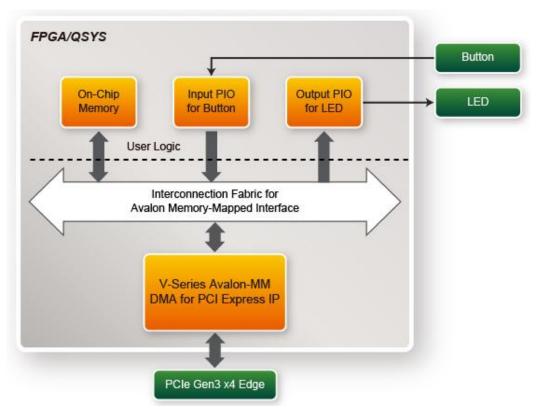

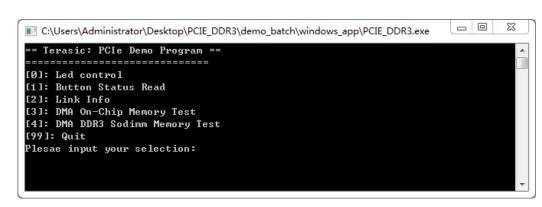

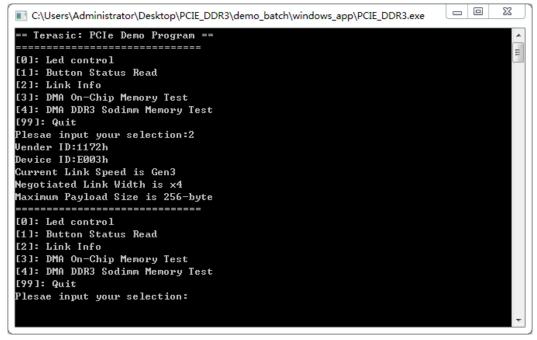

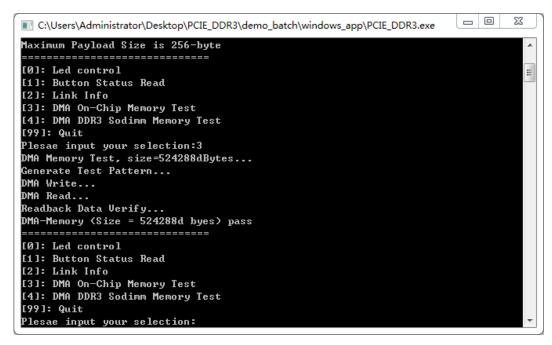

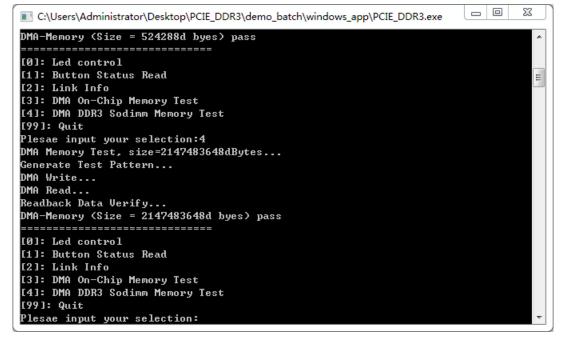

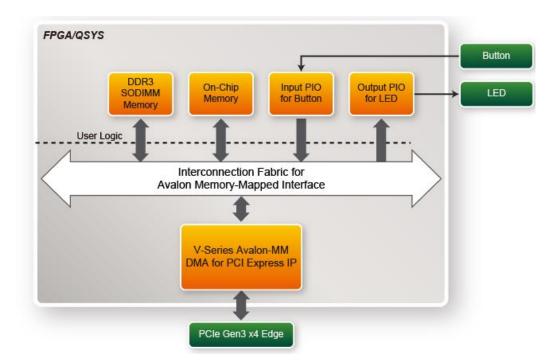

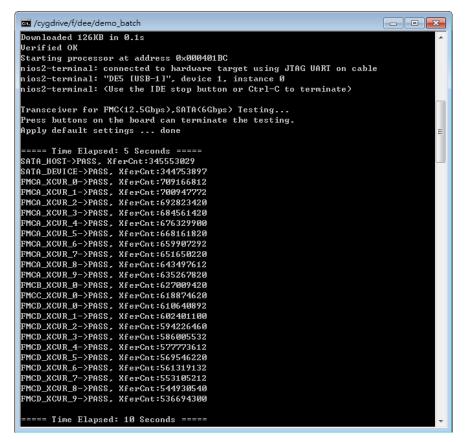

| 16<br>17<br>18<br>19<br>20                                                                                                                                                                                                                       | NC                                                                              | NC                                                                              | LA_TX_n3                                                                                                                                                                                       | GND                                                                                                                    | NC                                                                              | NC                                                 | LA_TX_p4                                                                                                                                                                 | LA_RX_p3                                                                     | NC                                                 | NC                                                 |