HERO Doucment Hardware Manual Chinese

From Terasic Wiki

(→以太网LAN端口) |

(→3.2 FPGA加速版卡功能方块图) |

||

| (22 intermediate revisions not shown) | |||

| Line 1: | Line 1: | ||

| - | = | + | =第1章 介绍= |

==1.1 概述== | ==1.1 概述== | ||

| Line 132: | Line 132: | ||

HERO平台的CPU主机系统,在外部提供了两个USB3.0的接口,每个接口的最大电流为900mA。 | HERO平台的CPU主机系统,在外部提供了两个USB3.0的接口,每个接口的最大电流为900mA。 | ||

:[[File:Hero USB 3.0 Ports.jpg|500px]] | :[[File:Hero USB 3.0 Ports.jpg|500px]] | ||

| - | :::::''' | + | :::::'''图 2-7 Hero USB 3.0端口''' |

| - | ===USB Type- | + | ===USB Type-C连接头=== |

| - | + | 端口支持Thunderbolt™3,最高达40Gbps的数据吞吐量,一个4K(60Hz)监视器输出,USB3.1(Gen 2)连接和5V/3A可达的充电功能。<br/> | |

| - | + | 它还支持DisplayPort 1.2规范,用于在高清晰度光盘播放器、机顶盒和电视显示器等消费电子设备之间的显示连接。支持的最大分辨率是4096 x 2304@60Hz,24bpp。 | |

:[[File:Hero USB Type-C Connector.jpg|500px]] | :[[File:Hero USB Type-C Connector.jpg|500px]] | ||

| - | :::::''' | + | :::::'''图 2-8 Hero USB Type-C连接头''' |

| + | |||

| + | =第三章 FPGA加速版卡= | ||

| + | |||

| + | ==3.1 FPGA加速板卡简介== | ||

| + | |||

| + | HERO平台内的FPGA加速板卡, 其主要目的为协同CPU主机系统做硬件计算加速功能. 鉴于现今许多工具平台的飞速发展, 使用FPGA板卡来加速已经不再繁琐耗时。 | ||

| + | |||

| + | 在人工智能应用领域,OpenVINO 工具包提供了良好的使用环境. FPGA加速卡在其中扮演着终端的角色, 当用户训练好的模型经过OpenVINO 工具包的推理最终能部署在FPGA加速卡上, 从而实现图像辨识算法加速功能。 | ||

| + | |||

| + | 用户也可以将FPGA加速卡用于OpenCL应用开发. 透过完整的FPGA板级支持包(Board Support Package), OpenCL工具能自动将用户边写好的OpenCL内核功能转换为定制FPGA硬件加速器,增加接口IP,构建互联逻辑,生成FPGA编程文件。熟悉C语言的系统开发人员和编程人员能够迅速方便的在高级语言环境中开发高性能、高功效、基于FPGA的应用。 | ||

| + | |||

| + | 当然,若用户有深厚的FPGA设计能力, 也可以自行的开发FPGA内各种加速逻辑, 对特殊应用完成硬件加速的目标。 | ||

| + | |||

| + | 为了能够支持上述的工具包(OpenVINO or OpenCL)运作, FPGA加速卡在系统开机时, 通常需要配置好相对应的接口逻辑, 如PCIe接口. 才能够与CPU主机系统进行数据传输。 | ||

| + | 因此,在CPU主机系统在开机时, FPGA加速板卡内的FPGA需要带有PCIe的功能配置, 确保能够与CPU主机系统交互并正常运作。 | ||

| + | |||

| + | 要达到此目,首先可以在FPGA加速板卡上的Flash需要先烧好带有PCIe功能的配置文件. FPGA板卡有电源提供时, 板上的系统控制器会去读取Flash内的配置文件并去配置FPGA。 | ||

| + | 或者在操作系统重新启动前, 先去下载好带有PCIe功能的配置文件(.sof 文件). 让系统重启后能找到FPGA加速卡的PCIe功能. 之后用户的应用逻辑可以在CPU主机系统透过PCIe接口对FPGA进行下载配置。 | ||

| + | |||

| + | 若是用户在操作系统内没有发现FPGA加速卡的PCIe设备, 代表可能FPGA加速卡并没有配置好带有PCIe的配置文件, 需检查Flash是否有或者刻录了正确的配置文件。 | ||

| + | |||

| + | ==3.2 FPGA加速版卡功能方块图== | ||

| + | |||

| + | |||

| + | 图3-1为FPGA加速系统的主要组件与CPU主机系统连接区块图 | ||

| + | |||

| + | :[[File:Hero FPGA acceleration system block diagram 1.jpg|700px]] | ||

| + | |||

| + | '''图3-1 FPGA 加速卡组件框图''' | ||

| + | |||

| + | ==3.3 USB Blaster II Port== | ||

| + | |||

| + | USB Blaster II port 的最主要目的是FPGA配置,它允许用户从操作系统把设计好的FPGA配置文件(主要为.sof file)透过USB接口以JTAG协议来配置FPGA。 | ||

| + | 从而,使FPGA能够依照使用者设计来运作. USB blaster II 电路内建在FPGA加速板卡上, 让使用者无须再外接下载器。此外,注意在使用这个USB blaster II电路之前, | ||

| + | 在操作系统需安装驱动装置(在安装好的Qaurtus软件内), 但在出厂的HERO平台已经先安装完成. | ||

| + | |||

| + | :[[File:Hero USB Blaster II Port.jpg|500px]] | ||

| + | |||

| + | '''图3-2 FPGA加速卡上USB Blaster II 接口''' | ||

| + | |||

| + | 使用时, 将一条Mini USB数据线, 把这个接口与CPU主机系统的USB接口相连接即可。 | ||

| + | |||

| + | [[File:Hero_HD_f3-3-cable.png|400px]] | ||

| + | |||

| + | '''图3-3 连接USB Blaster II Port 至CPU主机系统''' | ||

| + | |||

| + | 在HERO平台中, 由于可以搭配OpencL或者OpenVNIO工具包, 让用户可以直接从操作系统透过PCIe接口去配置FPGA, 因此,会使用到USB Blaster II 接口的时机比较少。 | ||

| + | |||

| + | 主要有下面几个情况会使用到个接口: | ||

| + | |||

| + | i . 若使用者想更换或升级FPGA加速卡内的Flash的配置文件, 需要透过这个USB Blaster 接口去更新板子上的Flash. | ||

| + | |||

| + | ii. 使用者想要自行设计FPGA加速板卡内的所有设计, 不需其他的工具包辅助. 此时便可当一般的FPGA板卡使用, 设计完成的FPGA配置文件透过这个USB Blaster下加载FPGA内,完成配置。 | ||

| + | |||

| + | iii. 当刻录在Flash内的默认OpencL配置文件版本跟要运行的.aocx版本不同, 导致无法透过PCIe去配置FPGA时, 也可以透过USB Blaster去下载, 让FPGA运行使用者想要的状态。 | ||

| + | |||

| + | ==3.4 DDR4内存== | ||

| + | |||

| + | FPG加速板上提供了四颗总容量共2GB的DDR4器件(见图2-x). 可用于数据缓存使用. 可使用的位宽最大为64bit并在2400Mhz(I1 速度等级的FPGA)频率下运行. 最大的理论带宽为153.6Gbps. 详细的FPGA对于DDR4的I/O管脚分配如表2-x。 | ||

| + | |||

| + | [[File:Hero_HD_f3-4-DDR4.jpg|600px]] | ||

| + | |||

| + | '''图3-4 DDR4与FPGA连接图''' | ||

| + | |||

| + | ==3.5 PCIe 接口== | ||

| + | |||

| + | FPGA加速系统板上带有一个PCIe Gen 3 x4的接口可用于连接于CPU主机系统。利用Arria 10 GX器件上的内置收发器与集成的PCI Express硬核IP模块, 能够提供完整的PCI Express解决方案。 | ||

| + | |||

| + | 在HERO平台内,透过OpenCL或者 OpenVINO工具包的协助, CPU主机系统可透过PCIe接口去配置FPGA完成加速逻辑. 并且传送或取回各种运算加速的数据. | ||

| + | |||

| + | |||

| + | ==3.6 USB 3.0 主设备(Host)== | ||

| + | |||

| + | FPGA加速版上保留了一颗 USB 3.0兼容的xHCI Host 控制器(TI :TUSB7320IRKM), 搭配了两个USB 3.0 Standard-A接口. | ||

| + | 预期能让FPGA加速板可以提供两个USB 3.0 Host的功能. '''注意, 此功能目前为保留设计, 尚无法使用'''. | ||

| + | TUSB7320IRKM 控制器与FPGA连接的接口遵从PCIe x1 Gen2 协议.所以,需将两者间用一对TX/RX的transceiver相连接。 详细的控制器信息可以参考CD内的Datasheet文件夹中tusb7320.pdf文件。 | ||

| + | |||

| + | [[File:Hero-HD-f3-5USBHOST_2.jpg|400px]] | ||

| + | |||

| + | '''图3-5 FPGA加速卡USB3.0主设备''' | ||

| + | |||

| + | ==3.7 USB 3.0 从设备(Device)== | ||

| + | |||

| + | FPGA加速板上放置了一颗Cypress型号为CYUSB3014的 USB 3.0控制器. 能提USB3.0 Device端以及USB2.0 OTG的相关应用. 用户可以透过这个接口, 将FPGA与CPU主系统或者其他计算机主机进行USB3.0的数据传输。 | ||

| + | |||

| + | 更多详细的资料请参考CD内的Datasheet文件夹中FX3子文件夹。 | ||

| + | |||

| + | [[File:Hero-HD-f3-6USBDevice.jpg|400px]] | ||

| + | |||

| + | '''图3-6 FPGA加速卡USB3.0从设备''' | ||

| + | |||

| + | ==3.8 千兆以太网络 == | ||

| + | |||

| + | FPGA加速板上配置了一颗10/100/1000千兆位以太网收发芯片 MARVELL 88E1111。该芯片是一个自动协商的以太网PHY,使用默认的SGMII MAC接口与FPGA相连。 | ||

| + | 传输的形式为LVDS I/O, 速度为1.2Gbps。用户可以在FPGA内置入一个MAC IP.便可以让此加速板与外部设备使用Ethernet 进行通信。 | ||

| + | |||

| + | [[File:Hero-HD-f3-7NET.jpg|400px]] | ||

| + | |||

| + | '''图3-7 FPGA加速卡网口''' | ||

| + | |||

| + | ==2.8 时钟电路== | ||

| + | |||

| + | |||

| + | 如图x所示.FPGA加速板上有多个osc与 on board PLL提供时钟频率给FPGA进行多样的应用. 其中提供给 FPGA transceiver bank的 PLL 可以透过 I2C去改变输出的频率.以便满足其特殊需求. 其他输入FPGA的固定频率也被连接入专属的FPGA时钟输入管脚. 用户可以使用FPGA内部的PLL对输入频率进行倍频或者分频后使用。 | ||

| + | |||

| + | [[File:Hero-HD-f3-8clock.jpg|900px]] | ||

| + | |||

| + | '''图3-8 时钟框图''' | ||

| + | |||

| + | |||

| + | [[HERO_Doucment_Hardware_Manual|'''Back''']] | ||

Latest revision as of 14:27, 29 August 2019

Contents |

第1章 介绍

1.1 概述

HERO平台全称为Heterogeneous Extensible Robot Open Platform,是专为智能机器人(包括服务机器人、医疗机器人、自动驾驶汽车等)打造的一套低功耗、高性能、体积小的异构系统平台方案。在此方案中,CPU作为控制中心,与FPGA和其他专用加速器芯片(如Movidius的VPU)搭配,能够提供高效的性能。整套HERO硬件系统采用了英特尔酷睿?系列CPU,搭载英特尔Arria 10 GX系列1150型FPGA作为异构加速器。

传统的FPGA编程方式令多数软件工程师望而却步,而HERO平台为大家带来了福音。除了传统的专业编程模型,HERO平台专门定制的BSP(Board Support Package)还支持基于OpenCL的flow开发,给广大的算法和软件工程师提供了友好的编程接口。为了支持OpenCL Flow,HERO平台上移植了完整的FPGA板级支持包(Board Support Package),作为HERO SDK的一个组成部分提供给用户。现有HERO SDK BSP的FPGA逻辑部分主要包括高速通信接口PCIe IP核、内存DMA控制器、片外高速内存DDR4接口,以及和FPGA内部模块之间的通信接口。如果用户想增加FPGA与外部接口之间的通讯, HERO平台也有相应的BSP参考设计,能够指导客户更好、更快地实现各种灵活多变的外部接口。

HERO平台的应用前景广阔。以服务机器人为例,其主要作用是帮助人完成任务和动作。为了实现这一目标,研发人员需要在机器人上实现各种复杂的应用控制技术,包括视觉、定位、运动、抓取等。FPGA可以在这些关键应用上发挥极大的价值,让复杂算法的处理变得高效而实时,带给用户良好的体验。

1.2 技术规格

Hero平台有两个板卡组合而成,分别为 CPU 主机系统与 FPGA加速度系统(见图1-1)。两者以PCIe接口连接进行传输与通信, 完成CPU协同FPGA的各种计算加速、算法实现功能。FPGA系统使用Intel Arria10 FPGA PCIe板卡。下面将介绍这两大主板系统的各个参数规格:

- CPU主系统

- 处理器: 英特尔® 酷睿™ i5-7260U/i7-7567U(根据客户订单需求而定)

- 内存: DDR4-2133 1.2V SO-DIMM 8GB

- 硬盘: Sata SSD 256G

- 显卡

- 集成显卡

- 图像输出: HDMI 2.0a;USB-C (DP1.2)

- 外围接口

- USB Type C端口 x1

- Thunderbolt™ 3 (40Gbps)

- USB 3.1 Gen 2 (10Gbps)

- DisplayPort (DP 1.2)

- USB 3.0/2.0 端口x2

- 局域网: Gigabit (10/100/1000 Mb/s)局域网

- 无线: 英特尔® Wireless-AC 8265 + 蓝牙4.2

- FPGA加速系统

- FPGA: Altera Arria 10 GX FPGA (10AX115S2F45I1SG)

- FPGA配置电路

- 板载USB Blaster II或FPGA编程的JTAG接头

- 快速被动并行配置(FPPx32):通过MAX II CPLD和闪存

- 内存

- 256MB闪存

- 2GB DDR44 -2400 x 64bit

- 通信与扩展

- PCI Express (PCIe) x8 edge接头

- USB 3.0 Host/Device

- 以太网

- UART/CAN/SPI/I2C

- 通用用户输入/输出:

- 8 LEDs

- 3 Push-buttons

- 8 DIP Switch

- 时钟

- 50/100/125MHz固定时钟

- 可编程PLL

- 系统监测与控制

- 温度感应器

- 电源监测

第2章 系统接口介绍与说明

2.1 概述

HERO平台由CPU主机系统以及FPGA加速卡组合而成。如图2-1所示,平台上所对外的接口也分为两类。橙色线标注的外设接口为CPU主机系统接口,如HDMI、USB接口。能让运行在CPU主机系统上的操作系统使用鼠标或者有屏幕输出功能。

蓝色线条所标注的为FPGA加速卡上的外设接口。这些接口能让FPGA加速卡有扩充的外设能力,如连接以太网处理网络功能,但这些接口都需要用户自行在FPGA内做相对应的设计才可以使用。在出厂设定时并没有包含此类的设计。

另外,须注意此两类系统无法兼容使用,如连接FPGA加速卡的以太网口,无法使CPU主机系统拥有连通网络功能。同样在FPGA加速卡的USB接口连接上USB鼠标,无法使CPU主机系统侦测到鼠标功能。

图 2-1 HERO平台主要接口

下面我们将先介绍HERO平台上的电源以及CPU主机系统的接口。关于FPGA加速板卡的接口在第三章会有描述。

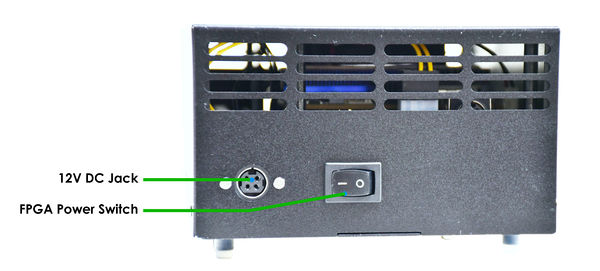

2.2 12V系统电源输入与FPGA电源开关

图 2-2为HERO平台的电源输入口与FPGA电源开关,需使用DC 12V电源供应器提供电源。FPGA电源开关为FPGA加速卡电源开关。使用HERO平台需先开启此处电源,好让FPGA先行供电并配置完成,以利后续CPU主机系统侦测FPGA加速卡设备。

图 2-2 12V系统电源输入与FPGA电源开关

2.3 CPU主机系统电源按钮

图2-3为CPU主机系统的电源按钮,按下此键可以开启CPU主机系统。如同大多数的PC机,在CPU主机系统电源开启的状态下(按钮将会出现蓝光),长按此按钮四秒钟将会强制关闭系统电源。只按一次,操作系统将会出现重启选项。

图 2-3 CPU主机系统电源按钮

2.4 CPU主机系统接口

这节将介绍CPU主机系统的外设接口。

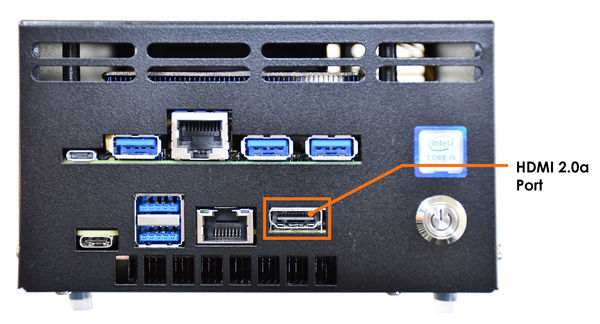

高清晰度多媒体接口(HDMI)

图 2-4 高清晰度多媒体接口

HDMI端口支持标准、增强或高清晰度视频,以及在单根电缆上的多通道数字音频。该端口兼容所有ATSC和DVB高清电视标准,支持24位/96 kHz内的8个全方位频道无损音频格式。支持的最大分辨率是4096 x 2160@60hz,24bpp.HDMI端口符合HDMI 2.0规范。

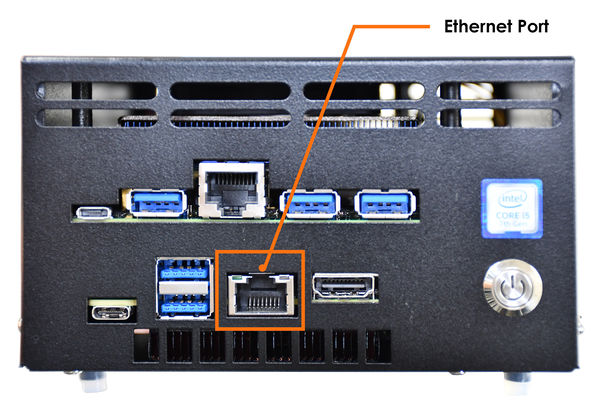

以太网LAN端口

图 2-5 以太网LAN端口

CPU主机系统上的以太网端口支持以下特性:

- 符合1Gb/s以太网802.3、802.3u、802.3z、802.3ab规格

- 多速度操作:10/100/1000 Mb/s

- 全双工操作10/100/1000 Mb/s;半双工操作10/100 Mb/s

- 流量控制支持符合802.3规格,以及802.3z定义的对称流量控制的具体操作

- VLAN支持符合802.3q规范

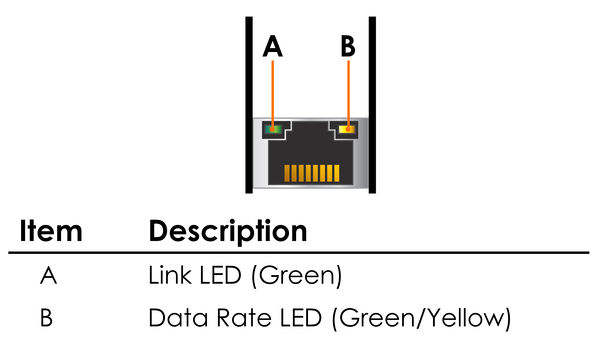

两个LED内置在RJ-45 LAN连接器中(见图2-6).

图 2-6 RJ-45 LAN连接器的LED

表 2-1 描述了板卡开机和局域网子系统运行时的LED状态。

表 2-1 LED状态描述

LED LED颜色 LED状态 LAN状态 连接 绿 熄灭 LAN连接没有建立 常亮 LAN连接建立 闪烁 LAN运行 数据速率 绿/黄 熄灭 选择10Mb/s数据速率 绿 选择100Mb/s数据速率 黄 选择1000Mb/s数据速率

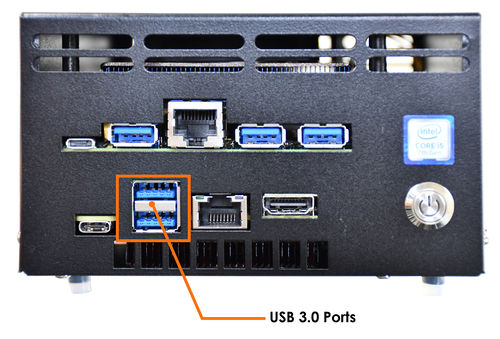

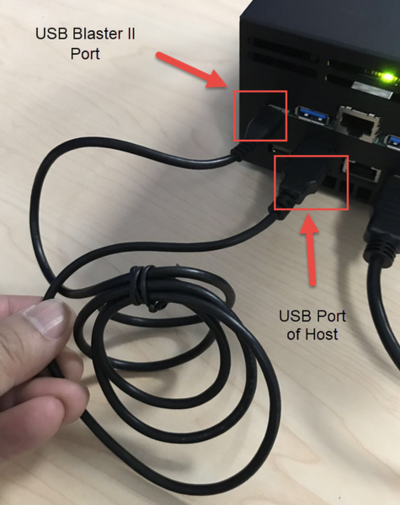

USB 3.0端口

HERO平台的CPU主机系统,在外部提供了两个USB3.0的接口,每个接口的最大电流为900mA。

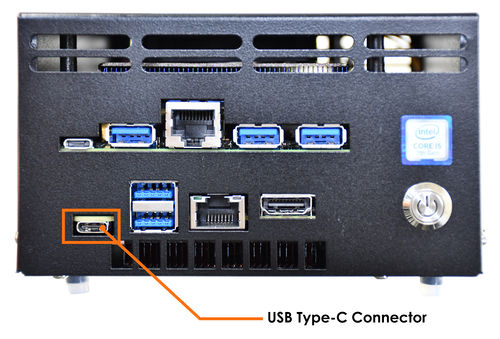

USB Type-C连接头

端口支持Thunderbolt™3,最高达40Gbps的数据吞吐量,一个4K(60Hz)监视器输出,USB3.1(Gen 2)连接和5V/3A可达的充电功能。

它还支持DisplayPort 1.2规范,用于在高清晰度光盘播放器、机顶盒和电视显示器等消费电子设备之间的显示连接。支持的最大分辨率是4096 x 2304@60Hz,24bpp。

第三章 FPGA加速版卡

3.1 FPGA加速板卡简介

HERO平台内的FPGA加速板卡, 其主要目的为协同CPU主机系统做硬件计算加速功能. 鉴于现今许多工具平台的飞速发展, 使用FPGA板卡来加速已经不再繁琐耗时。

在人工智能应用领域,OpenVINO 工具包提供了良好的使用环境. FPGA加速卡在其中扮演着终端的角色, 当用户训练好的模型经过OpenVINO 工具包的推理最终能部署在FPGA加速卡上, 从而实现图像辨识算法加速功能。

用户也可以将FPGA加速卡用于OpenCL应用开发. 透过完整的FPGA板级支持包(Board Support Package), OpenCL工具能自动将用户边写好的OpenCL内核功能转换为定制FPGA硬件加速器,增加接口IP,构建互联逻辑,生成FPGA编程文件。熟悉C语言的系统开发人员和编程人员能够迅速方便的在高级语言环境中开发高性能、高功效、基于FPGA的应用。

当然,若用户有深厚的FPGA设计能力, 也可以自行的开发FPGA内各种加速逻辑, 对特殊应用完成硬件加速的目标。

为了能够支持上述的工具包(OpenVINO or OpenCL)运作, FPGA加速卡在系统开机时, 通常需要配置好相对应的接口逻辑, 如PCIe接口. 才能够与CPU主机系统进行数据传输。 因此,在CPU主机系统在开机时, FPGA加速板卡内的FPGA需要带有PCIe的功能配置, 确保能够与CPU主机系统交互并正常运作。

要达到此目,首先可以在FPGA加速板卡上的Flash需要先烧好带有PCIe功能的配置文件. FPGA板卡有电源提供时, 板上的系统控制器会去读取Flash内的配置文件并去配置FPGA。 或者在操作系统重新启动前, 先去下载好带有PCIe功能的配置文件(.sof 文件). 让系统重启后能找到FPGA加速卡的PCIe功能. 之后用户的应用逻辑可以在CPU主机系统透过PCIe接口对FPGA进行下载配置。

若是用户在操作系统内没有发现FPGA加速卡的PCIe设备, 代表可能FPGA加速卡并没有配置好带有PCIe的配置文件, 需检查Flash是否有或者刻录了正确的配置文件。

3.2 FPGA加速版卡功能方块图

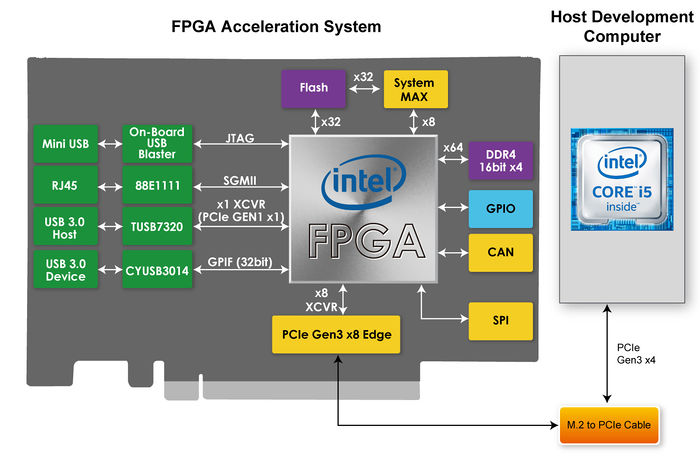

图3-1为FPGA加速系统的主要组件与CPU主机系统连接区块图

图3-1 FPGA 加速卡组件框图

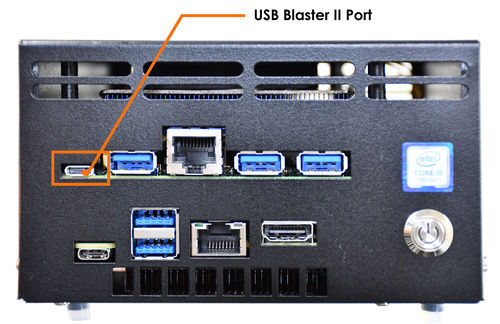

3.3 USB Blaster II Port

USB Blaster II port 的最主要目的是FPGA配置,它允许用户从操作系统把设计好的FPGA配置文件(主要为.sof file)透过USB接口以JTAG协议来配置FPGA。 从而,使FPGA能够依照使用者设计来运作. USB blaster II 电路内建在FPGA加速板卡上, 让使用者无须再外接下载器。此外,注意在使用这个USB blaster II电路之前, 在操作系统需安装驱动装置(在安装好的Qaurtus软件内), 但在出厂的HERO平台已经先安装完成.

图3-2 FPGA加速卡上USB Blaster II 接口

使用时, 将一条Mini USB数据线, 把这个接口与CPU主机系统的USB接口相连接即可。

图3-3 连接USB Blaster II Port 至CPU主机系统

在HERO平台中, 由于可以搭配OpencL或者OpenVNIO工具包, 让用户可以直接从操作系统透过PCIe接口去配置FPGA, 因此,会使用到USB Blaster II 接口的时机比较少。

主要有下面几个情况会使用到个接口:

i . 若使用者想更换或升级FPGA加速卡内的Flash的配置文件, 需要透过这个USB Blaster 接口去更新板子上的Flash.

ii. 使用者想要自行设计FPGA加速板卡内的所有设计, 不需其他的工具包辅助. 此时便可当一般的FPGA板卡使用, 设计完成的FPGA配置文件透过这个USB Blaster下加载FPGA内,完成配置。

iii. 当刻录在Flash内的默认OpencL配置文件版本跟要运行的.aocx版本不同, 导致无法透过PCIe去配置FPGA时, 也可以透过USB Blaster去下载, 让FPGA运行使用者想要的状态。

3.4 DDR4内存

FPG加速板上提供了四颗总容量共2GB的DDR4器件(见图2-x). 可用于数据缓存使用. 可使用的位宽最大为64bit并在2400Mhz(I1 速度等级的FPGA)频率下运行. 最大的理论带宽为153.6Gbps. 详细的FPGA对于DDR4的I/O管脚分配如表2-x。

图3-4 DDR4与FPGA连接图

3.5 PCIe 接口

FPGA加速系统板上带有一个PCIe Gen 3 x4的接口可用于连接于CPU主机系统。利用Arria 10 GX器件上的内置收发器与集成的PCI Express硬核IP模块, 能够提供完整的PCI Express解决方案。

在HERO平台内,透过OpenCL或者 OpenVINO工具包的协助, CPU主机系统可透过PCIe接口去配置FPGA完成加速逻辑. 并且传送或取回各种运算加速的数据.

3.6 USB 3.0 主设备(Host)

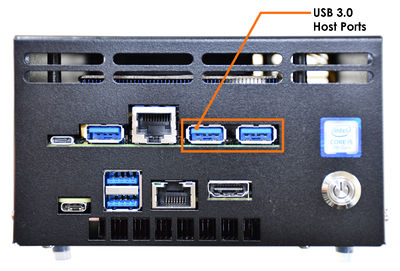

FPGA加速版上保留了一颗 USB 3.0兼容的xHCI Host 控制器(TI :TUSB7320IRKM), 搭配了两个USB 3.0 Standard-A接口. 预期能让FPGA加速板可以提供两个USB 3.0 Host的功能. 注意, 此功能目前为保留设计, 尚无法使用. TUSB7320IRKM 控制器与FPGA连接的接口遵从PCIe x1 Gen2 协议.所以,需将两者间用一对TX/RX的transceiver相连接。 详细的控制器信息可以参考CD内的Datasheet文件夹中tusb7320.pdf文件。

图3-5 FPGA加速卡USB3.0主设备

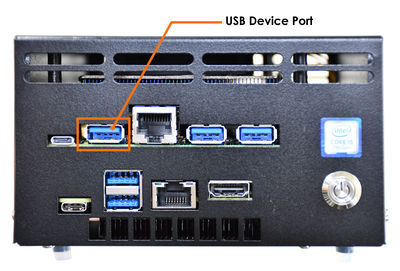

3.7 USB 3.0 从设备(Device)

FPGA加速板上放置了一颗Cypress型号为CYUSB3014的 USB 3.0控制器. 能提USB3.0 Device端以及USB2.0 OTG的相关应用. 用户可以透过这个接口, 将FPGA与CPU主系统或者其他计算机主机进行USB3.0的数据传输。

更多详细的资料请参考CD内的Datasheet文件夹中FX3子文件夹。

图3-6 FPGA加速卡USB3.0从设备

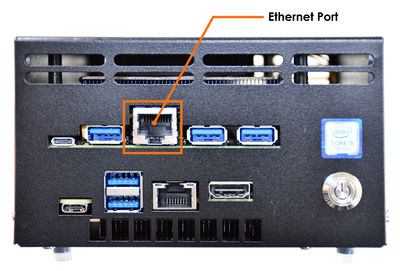

3.8 千兆以太网络

FPGA加速板上配置了一颗10/100/1000千兆位以太网收发芯片 MARVELL 88E1111。该芯片是一个自动协商的以太网PHY,使用默认的SGMII MAC接口与FPGA相连。 传输的形式为LVDS I/O, 速度为1.2Gbps。用户可以在FPGA内置入一个MAC IP.便可以让此加速板与外部设备使用Ethernet 进行通信。

图3-7 FPGA加速卡网口

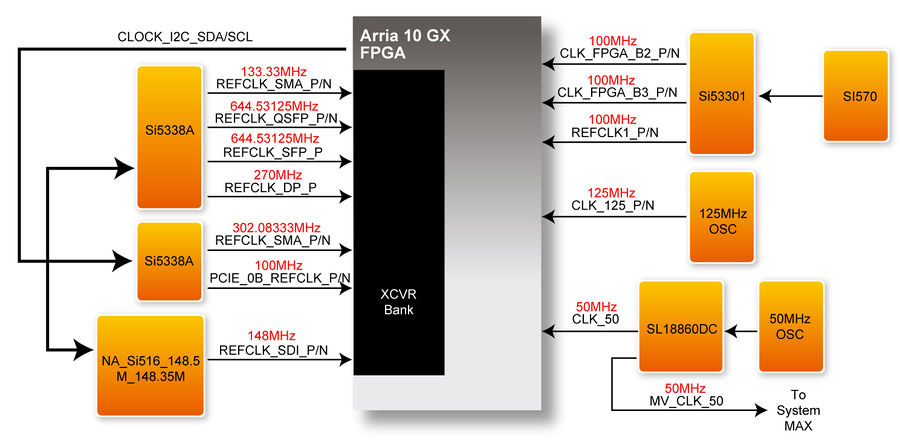

2.8 时钟电路

如图x所示.FPGA加速板上有多个osc与 on board PLL提供时钟频率给FPGA进行多样的应用. 其中提供给 FPGA transceiver bank的 PLL 可以透过 I2C去改变输出的频率.以便满足其特殊需求. 其他输入FPGA的固定频率也被连接入专属的FPGA时钟输入管脚. 用户可以使用FPGA内部的PLL对输入频率进行倍频或者分频后使用。

图3-8 时钟框图