F2G User Manual

From Terasic Wiki

(→1-4 Block Diagram) |

(→1-4 Block Diagram) |

||

| Line 32: | Line 32: | ||

=1-4 Block Diagram= | =1-4 Block Diagram= | ||

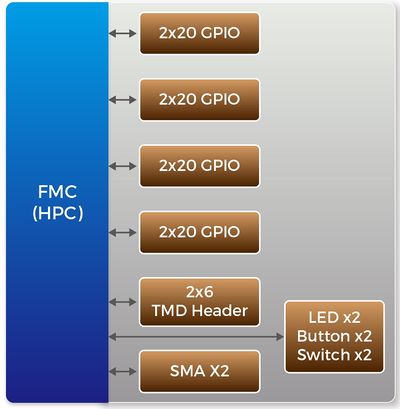

Figure 1-5 gives the block diagram of the board. | Figure 1-5 gives the block diagram of the board. | ||

| + | <div style="text-align:center;color:#ff0000;"> [[Image: F2G BlockDiagram.jpg|400px]]</div> | ||

| + | <div style="text-align:center;"> '''Figure 1‑5 Block diagram of the F2G board'''</div> | ||

= 1-2 Getting Help = | = 1-2 Getting Help = | ||

Revision as of 18:05, 11 May 2020

Contents |

Chpater1 Introduction

The F2G board is designed to convert a FPGA Mezzanine Card(FMC) or FPGA Mezzanine Card Plus(FMC+) interface to four 2x20pin expansion prototype(GPIO) connectors, which are compatible with the expansion headers of the Terasic DE-Series board(Such as DE2-115/DE10-Standard). Users can connect up to four GPIO connectors onto a FMC-interfaced host board via a F2G board.

1-1 Kit Contents

Figure 1-1 shows a photograph of the F2G package.

- F2G Card

- Screw & Copper Pillar Pakage

- CD Download Guide

1-2 Features

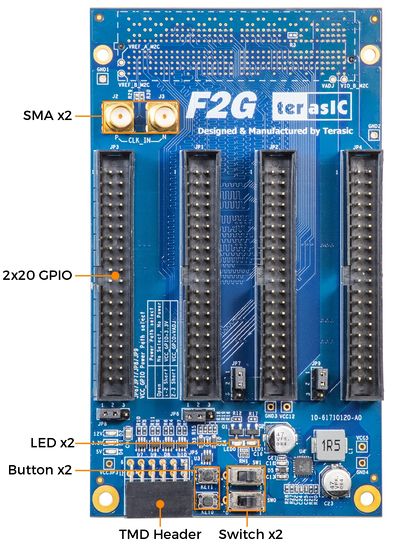

Figure 1-2 shows the photo of a F2G board. The important functions of the F2G are listed below:

- FMC High-Pin Count Interface.

- IO standard is dependent on FMC Voltage of the Mother board.

- Four 2x20 GPIO Headers.

- 2x6 TMD Header.

- SMA Clock Input.

- Button x2.

- SWtich x2.

- LED x2.

1-3 Layout and Components

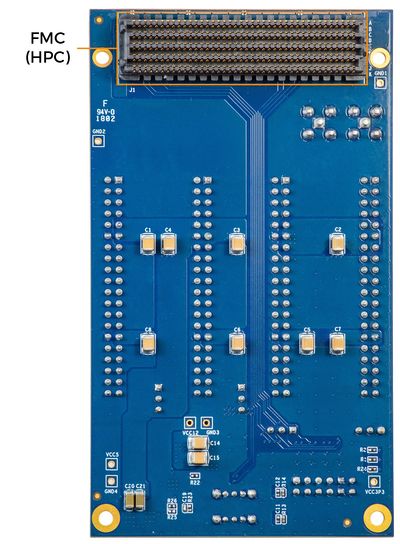

This section presents the features and design characteristics of the board. A photograph of the board is shown in Figure 1-3 and Figure 1-4 It depicts the layout of the board and indicates the location of the connectors and key components.

1-4 Block Diagram

Figure 1-5 gives the block diagram of the board.

1-2 Getting Help

Contact us via the following methods for further technical assistance:

- Terasic Inc.9F, No.176, Sec.2, Gongdao 5th Rd, East Dist, Hsinchu City, Taiwan 300-70

- Email : support@terasic.com

- Web : www.terasic.com