F2G with intel A10GFP

From Terasic Wiki

(→GPIO Uisng Status) |

(→GPIO Uisng Status) |

||

| Line 10: | Line 10: | ||

On the Kit board, some FPGA I/Os connected to the F2G GPIO connector will have termination resistors(for differential protocol). It is recommended to remove these resistors, otherwise the pins of the GPIO connector will interfere with each other when using in single-end state. | On the Kit board, some FPGA I/Os connected to the F2G GPIO connector will have termination resistors(for differential protocol). It is recommended to remove these resistors, otherwise the pins of the GPIO connector will interfere with each other when using in single-end state. | ||

| + | <div style="text-align:center;color:#ff0000;"> [[Image: F2g a10gfp 02.jpg|900px]]</div> | ||

<noinclude> | <noinclude> | ||

[[Category:F2G]] | [[Category:F2G]] | ||

</noinclude> | </noinclude> | ||

Revision as of 17:30, 18 June 2020

This document will introduce what you need to pay attention to when the Terasic F2G card is connected to Intel Arria® 10 GX FPGA Development Kit.

GPIO Uisng Status

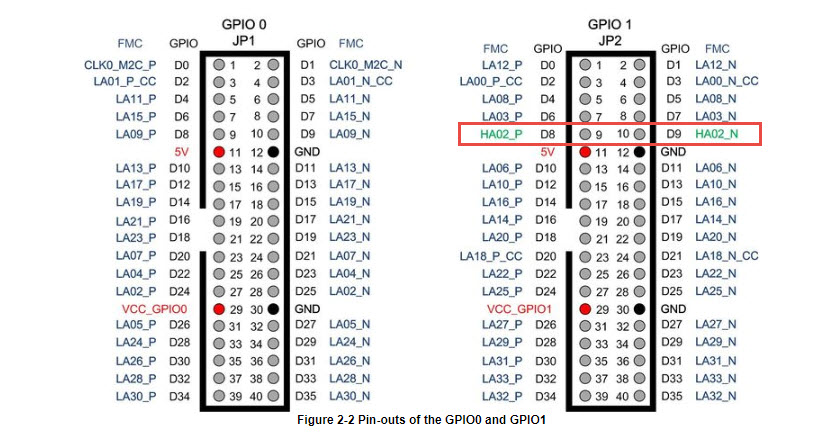

Due the two FMC connectors FMCA and FMCB on the Arria® 10 GX FPGA Development Kit belong to the low pin count(LPC) FMC type(Note), after connecting the F2G card, only the two connectors GPIO 0 and GPIO 1 on the F2G card can be used on the kit, and the other two GPIO connectors are defined Connected to high pin count(HPC) FMC pin, so it cannot be used in the kit. In addition, the D8/D9 pin on GPIO 1 belongs to the HPC FMC type, so it cannot be used.

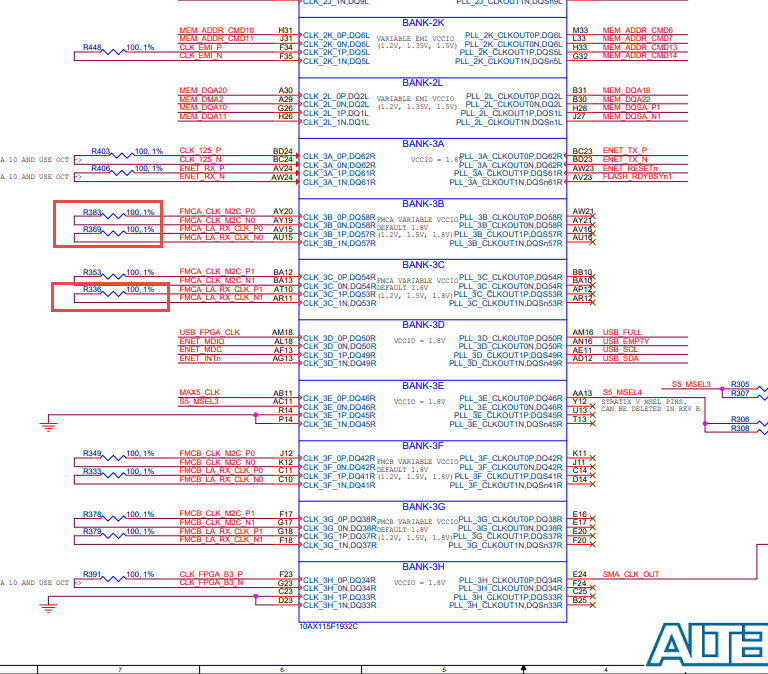

On the Kit board, some FPGA I/Os connected to the F2G GPIO connector will have termination resistors(for differential protocol). It is recommended to remove these resistors, otherwise the pins of the GPIO connector will interfere with each other when using in single-end state.