DE10-Agilex Board Revision Document

From Terasic Wiki

(Difference between revisions)

(→Rev. A to Rev. B) |

(→Rev. A to Rev. B) |

||

| Line 14: | Line 14: | ||

#: | #: | ||

#:[[File:De ag sw1.jpg|400px]] | #:[[File:De ag sw1.jpg|400px]] | ||

| - | #Add System MAX10 Jtag bypass switch (SW9) for increase JTAG sacn speed. | + | #Add System MAX10 Jtag bypass switch '''(SW9)''' for increase JTAG sacn speed. |

#: | #: | ||

#:[[File:De ag sw9.jpg|400px]] | #:[[File:De ag sw9.jpg|400px]] | ||

Revision as of 14:28, 26 February 2021

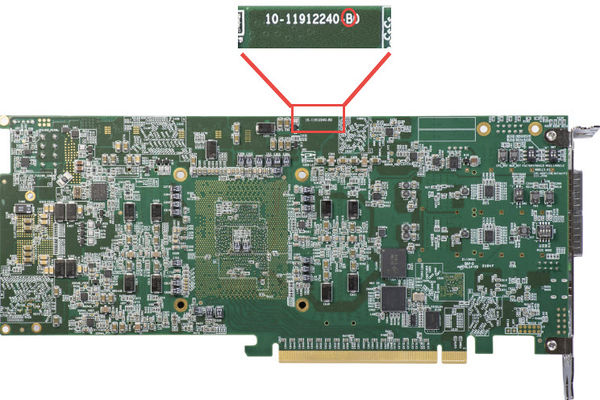

How to Find the DE10-Aiglex Board Revision?

On the bottom view of the PCB, there is a seal mark for the board hardware version.

As shown in the figure below, if the letter inside the red circle is "B", it means that the PCB version is Rev.B.

Board Revision Details

Rev. A to Rev. B

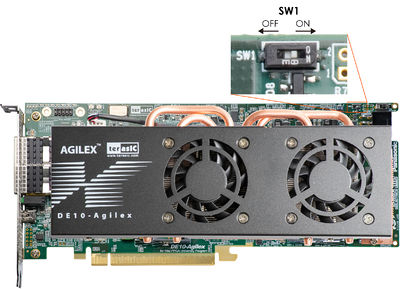

- Add Force External Power Switch (SW1) to Enable/Disable External Power Requirement when connected to the HOST PC.

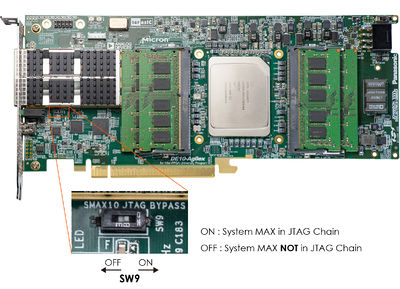

- Add System MAX10 Jtag bypass switch (SW9) for increase JTAG sacn speed.

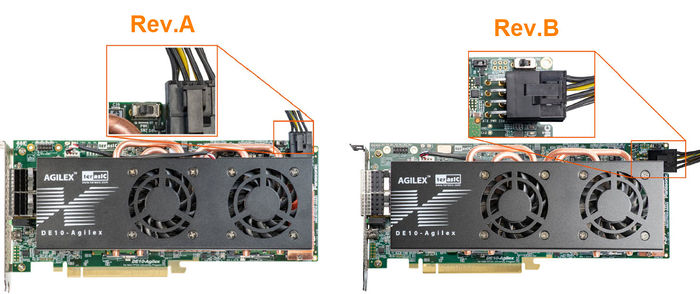

- Modify the direction of the external power connector.

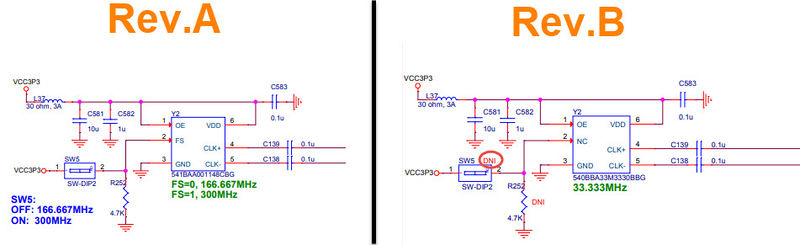

- Remove DDR4 Clock Source Switch (SW5) and change the DDR4 source clock oscillator (Y2) from dual clock OSC to 33.333Mhz OSC.