Prof. Russell Tessier, Head of Electrical and Computer Engineering at UMass Amherst, examines the DE25-Standard’s advancements in FPGA architecture, SoC integration, and classroom usability.

|

|

Technical Review Article

As a longtime user of Altera/Terasic products, I eagerly awaited the arrival of our new DE25-Standard Board. I have been using previous Terasic boards (notably the DE2 and the DE1-SoC) in my research and courses for nearly twenty years and I have found the products to be useful and robust. The DE25-Standard is particularly interesting as a low-cost FPGA board given the presence of the Altera (yes, the name is back) Agilex-5 SoC FPGA. In addition to enhanced FPGA logic, this device includes four ARM processor cores (hard processor system or HPS) with new features that enhance the classroom experience for students, as I will describe below.

The DE25-Standard includes most of the features of its predecessors, the DE1-SoC and DE10-Standard, with some interesting new features such as HDMI and USB-C interfaces. The board comes with a power cable and a USB cable with Type A and Type C connectors on opposite ends. Supporting software is available via download. This software includes datasheets for on-board components, demonstration files that can be executed on the board, manuals, board schematics, and a dashboard tool that runs on Windows and shows the state of on-board sensors during board execution. The user manual is particularly useful in describing board operation, especially board bootup via JTAG. Setting up the DE25 is simple: Just plug it into the power supply and attach the provided USB cable. The board's LEDs light up when booted from an SD card a provided Linux image.

The DE25-Standard includes a robust set of peripheral interfaces. FPGA-connected interfaces include push buttons, seven-segment displays, an audio codec, composite video in, HDMI 2.0 out, infrared (IR) send/receive, MIPI camera interface, and an HSMC connector. HPS-connected interfaces include USB 2.0, 10/100/1000 Mbps Ethernet, micro SD, an LCD module, and a G-sensor. 1 GB of DDR4 DRAM can be accessed by both the FPGA and HPS portions of the Agilex-5. The HDMI interface with 1080p resolution is of particular interest since it is new to the DE25-Standard. One of the provided demonstrations allows mirroring of the board’s component video input to the HDMI interface and a video display. My students were able to modify the provided HDL design and compile it into a bitstream to output a fixed image. The HDMI interface replaces the VGA port on the DE10-Standard and better fits with today’s video displays.

The new USB-C interface is an upgrade over the USB mini-B port found on the DE10-Standard. The port serves as a USB Blaster II programming interface and as a USB to UART interface for the HPS and on-board sensors (temperature, power, and fan speed). HSMC connections to the new board will require some changes from previous DE boards. FPGA I/O using the HSMC connector must be single-ended due to the interface pins used on the Agilex-5 SoC. A full comparison between the capabilities of the DE25-Standard and the DE10-Standard can be seen in the following table.

| Board | DE25-Standard | DE10-Standard |

|---|---|---|

| FPGA | Agilex™ 5 SoC FPGA : A5ED013BB32AE4S | Cyclone V SoC 5CSXFC6D6F31C6N |

| HPS | ARM Cortex processor with 2xA55 and 2xA76 | Dual-core ARM Cortex-A9 |

| Logic elements | 138K | 110K |

| Embedded Memory | 8.42 Mbits | 5.76 Mbits |

| Configuration | ASx4 configure mode with 128 Mbits of QSPI flash | Quad serial configuration device – EPCS128 on FPGA |

| Onboard USB-Blaster II | USB Type-C connector | USB Type-B connector |

| SDRAM | 1GB (2x256Mx16) DDR4 SDRAM shared with HPS | 1GB (2x256Mx16) DDR3 SDRAM on HPS |

| UART to USB | USB Type-C connector | USB Mini-B connector |

| Display Port | HDMI 2.0 Output Port (Support 1080P) | 24-bit VGA DAC |

The Agilex-5 SoC includes several new features that can greatly enhance student projects. All four ARM hard processor cores (two A76 cores and two A55 cores) include cryptographic extensions to their instruction sets. These extensions allow the processor cores to execute instructions that modify many data values in parallel. These types of software operations accelerate encryption algorithms such as the Advanced Encryption Standard (AES) and SHA-256. On the FPGA side, the multiplier blocks have been upgraded to better perform arithmetic operations suited to artificial intelligence (AI) applications. Each block can perform up to ten multiply operations followed by an accumulation of the products. The resulting integer value can then be converted to floating point. As a proof of concept, we successfully implemented a circuit that performs two 32-bit multiplications followed by an addition of the products in a single multiplier block. The output was displayed using LEDs.

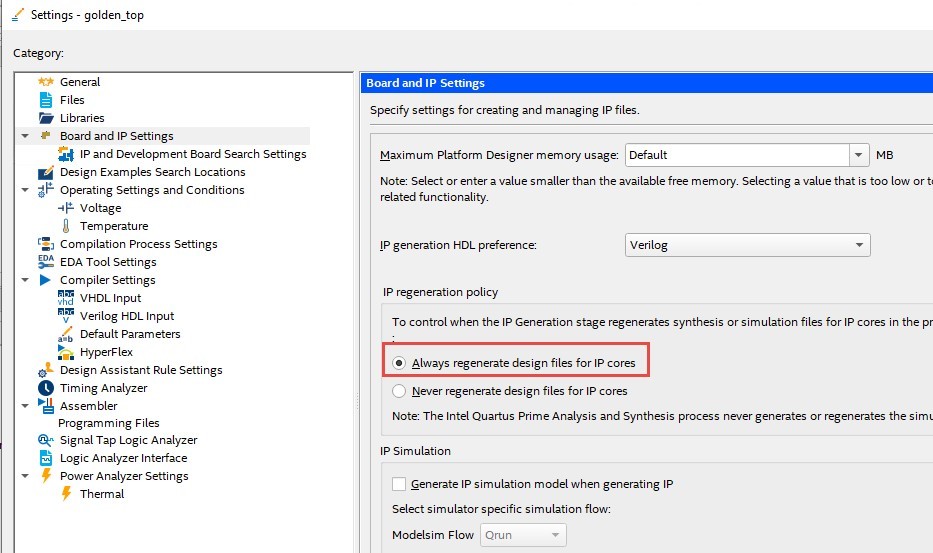

We were able to successfully compile and run all FPGA and SoC designs provided with the DE25-Standard distribution. These designs exercise the HDMI, IR, analog-to-digital converter, G-sensor, DRAM, and audio interfaces, among others. The designs provide a good starting point for student projects. We ran into a small issue using some of the designs which require intellectual property (IP), although the issue was quickly addressed by enabling the “Always regenerate design file for IP cores” flag in Quartus, as shown below.

While overall the DE25 is easy-to-use and robust, we did notice a few small issues during experimentation. Bitstream downloading to the board using batch files is more easily accomplished using Windows versus Linux, and the Dashboard application only works in Windows. Meanwhile, the cross compiler for the ARM cores requires the installation of the Windows subsystem for Linux (WSL) on the host workstation if Windows is used, a feature not needed for cross compilation on a Linux platform. These issues can easily be overcome.

Overall, our experience with the DE25-Standard has been very positive. We especially look forward to using the new AI and cryptographic extension features in the Agilex-5 FPGA SoC in future student projects. This board is a worthy successor to the very successful DE1-SoC and DE10-Standard platforms.

About the Author

Dr. Russell Tessier

Head of Electrical and Computer Engineering, University of Massachusetts, Amherst

Zhehang Zhang

Department of Electrical and Computer Engineering, University of Massachusetts, Amherst

Tianxu Li

Department of Electrical and Computer Engineering, University of Massachusetts, Amherst