Evaluation Kit Contents

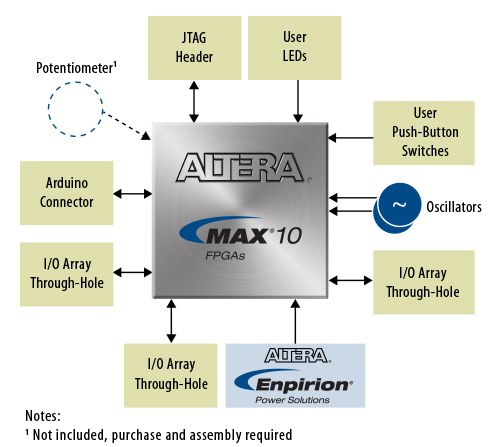

The Intel® MAX® 10 FPGA – 10M08 Evaluation Kit includes the following:

- CE-compliant Intel®

MAX®

10 evaluation board

- Intel® MAX® 10 FPGA (10M08, single power supply, 144-pin EQFP)

- Intel® Enpirion® EP5388QI point-of-load, 800 mA, DC-DC step-down (buck) converter with an integrated inductor

- JTAG header for download cable programming (POF) or configuration (SOF)

- 50 MHz single-ended, external oscillator clock source

- Shunt resistors and probe points to measure FPGA power

- Switch, push buttons, jumpers, and status LEDs

- Connectors:

- Arduino headers to accept UNO R3 compatible Shields

- General-purpose through-hole vias

- Type mini-B USB connector (power source)

- USB cable included

- Footprint to install a potentiometer (customer must purchase and install)

- Intel® MAX® 10 FPGA (10M08, single power supply, 144-pin EQFP)

- Free Intel® Quartus® Prime Lite Edition software (download and license from website)

- Complete documentation

- User manual, bill of materials, schematic, and board files

MAX 10 FPGA Evaluation Board Block Diagram