《DE1-SoC 每日一问》

From Terasic Wiki

1. Q:在下载自己设计工程的 jic 文件到DE1-SOC开发板后,打算再次下载时候,点击Programmer窗口的 Auto Detect 菜单,会提示:"Unable to scan device chain. Hardware is not connected",这是为什么呢?

A: 可能是您设计里面的pin assignment存在不合理。遇到这种情况,您可以通过用官网的文件(比如default案例的jic文件)覆盖您原先固化的自己的jic文件来解决。 具体操作如下:

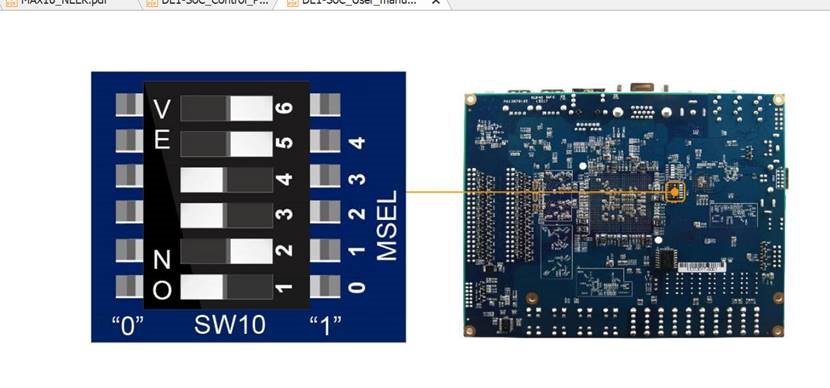

(1)请将MSEL改为00000模式

(2)下载default案例(DE1_SoC_Default)里面的sof文件。如果下载成功,请接着将MSEL设置成10010模式后,下载 default 案例中的 jic 文件到板子上。

(3)如果您需要继续下载自己工程的 jic 文件,建议您先修改设计哦。关于引脚分配部分,您可以参考友晶官网上System CD里面的案例。

2. Q: DE1-SOC开发板的Control Panel 工具与其他FPGA开发板的Control Panel 工具有哪些不同呢?

A: (1)DE1-SOC 的Control Panel 程序是基于QT库设计的,不带SOC的普通FPGA开发板的Control Panel是用Borland C++ Builder设计的。

(2)DE1-SOC的 Control Panel 通过AXI总线来操纵 FPGA端资源,在开发板linux上运行; 不带SOC的普通FPGA开发板的Control Panel程序是通过USB Blaster 线缆连接到 PC 机后在Windows上运行的。

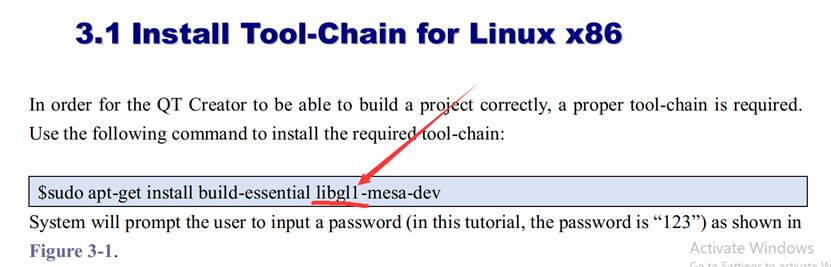

3. Q: 参考DE1-SoC_Control_Panel.pdf文档安装 x86 GCC tool-chain,输入"sudo apt-get install build-essential libgll

-mesa-dev"时提示:"Command line option 'e' [from -mesa] is

not understood in combination with the other options",这是什么原因呢?

A:这是您的命令输入错误导致的,应该是"libgl1",而不是"libglI"哦。如下图。

4. Q:DE1-SoC和D5M摄像头,该怎样搭配使用呢? 有没有参考例程呢?

A:如果您没有Quartus license,建议您参考这个例程来实现FPGA视频数据处:(http://mail.terasic.com.cn/~dongliu/DE1_SOC/DE1_SoC_D5M_GPIO1.zip) 通过该例程测试时的搭建硬件可以参考D5M SystemCD 中的user manual 里的DE1开发板硬件搭建小节。

如果您对画质的要求稍微高一些,且有Quartus license(或者VIP IP license),您还可以参考这个例程:(http://mail.terasic.com.cn/~dongliu/DE1_SOC/DE1_SoC_D5M_VIP.rar. )

5. Q:DE1-SOC的UART接口可以用FPGA去控制收发信号吗?

A: DE1-SOC的 Uart口是HPS端的硬件, 一般我们不建议FPGA端去控制,因为该实现过程比较复杂。

当您需要PGA端有串口的话, 可以直接用FPGA端的GPIO模拟一个Uart,这样实现起来会相对更简单一些哦。

6. Q: 想在SignalTap 里面拉DE1-SOC 开发板的Uart口信号时发现查看不到串口信号。 但是Uart口确实可以收发数据,这是为什么呢?

A:这是因为 SignalTap 是应用在FPGA端的工具,HPS是硬核,而串口是HPS端的硬件,所以SignalTap里面添加不了Uart信号

7. Q: DE1-SoC GPIO 能否设定为2.5V呢?是否支持LVDS信号传输呢?

A: DE1-SoC GPIO所对应的 FPGA I/O bank 的VCCIO电压是固定的3.3V,因此只能做3.3V信号传输使用。如果要接2.5V 外设, 可以尝试自行设计电平转换电路哦。

另外,DE1-SoC GPIO并没有做LVDS走线,所以也无法支持LVDS信号传输。

8. Q:在固化DE1-SOC的EPCQ256时,已成功生成 jic 文件,但下载时却提示“209025 Can't recognize silicon ID device 2”,这是哪一步操作错了吗?

![]()

A: 这是您的DE1-SOC开发板的MSEL设置错误导致的。请将MSEL正确设置到"10010"哦,具体如下图:

9. Q:使用DE1_SOC 开发板做一个nios II 的工程时,参考光盘的DE1_SoC_SDRAM_Nios_Test的例程进行操作,但是SDRAM运行不是很稳定。请问是否有DE1-SOC SDRAM相关的时序约束方面的参考?

A: 您可以参考友晶2014年DE1-SOC中文培训资料工程de1_soc_traning\de1_soc_traning\lab \Advanced_Demo\demo1_axi里的时序。该工程下载地址:http://www.myfpga.org/discuz/forum.php?mod=viewthread&tid=196841

10. Q:在运行Linux 桌面系统时,如何正确关闭Linux系统和开发板呢?

A:DE1-SOC 没有硬件提供power down 机制, 所以您只需在Linux关机( shut down )进入黑屏界面后给直接开发板断电就行呢。