DE10-Advance Hardware Manual revC Chapter4 Gigabit Ethernet

From Terasic Wiki

4.8 Gigabit Ethernet

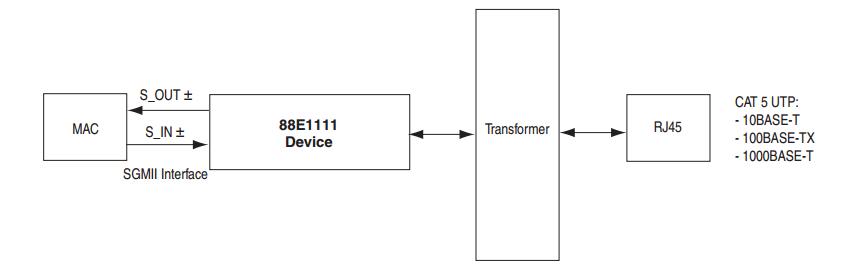

The development board supports one RJ45 10/100/1000 base-T Ethernet using Marvell 88E1111. SGMII AC coupling interface is used between PHY and FPGA transceiver.The device is an auto-negotiating Ethernet PHY with an SGMII interface to the FPGA. The Arria 10 SoC FPGA can communicate with the LVDS interfaces at up to 1.6 Gbps, which is faster than 1.25 Gbps for SGMII. The MAC function must be provided in the FPGA for typical networking applications. The Marvell 88E1111 PHY uses 2.5-V and 1.1-V power rails and requires a 25MHz reference clock driven from a dedicated oscillator. It interfaces to an RJ-45 with internal magnetics for driving copper lines with Ethernet traffic.Figure 4-2 shows the SGMII interface between the FPGA and Marvell 88E1111 PHY. Table 4-2 lists the Ethernet PHY interface pin assignments.

- Table 4-2 Ethernet PHY Pin Assignments, Signal Names and Functions

Signal Name FPGA Pin Number Description I/O Standard ETH_TX_p PIN_AP19 SGMII TX data LVDS ETH_RX_p PIN_AM20 SGMII RX data LVDS ETH_INT_n PIN_AU19 Management bus interrupt 1.8V ETH_MDC PIN_AT19 Management bus control 1.8V ETH_MDIO PIN_AJ20 Management bus data 1.8V ETH_RST_n PIN_AK20 Device reset 1.8V