DE10-Advance Hardware Manual revC Chapter6 System Clocks

From Terasic Wiki

Chapter 6 System Clocks

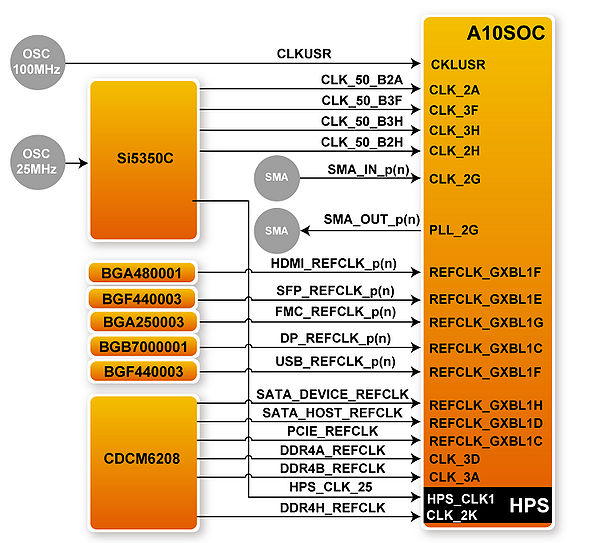

Figure 6-1 shows the Clock Net connected to FPGA on DE 10-Advanced.

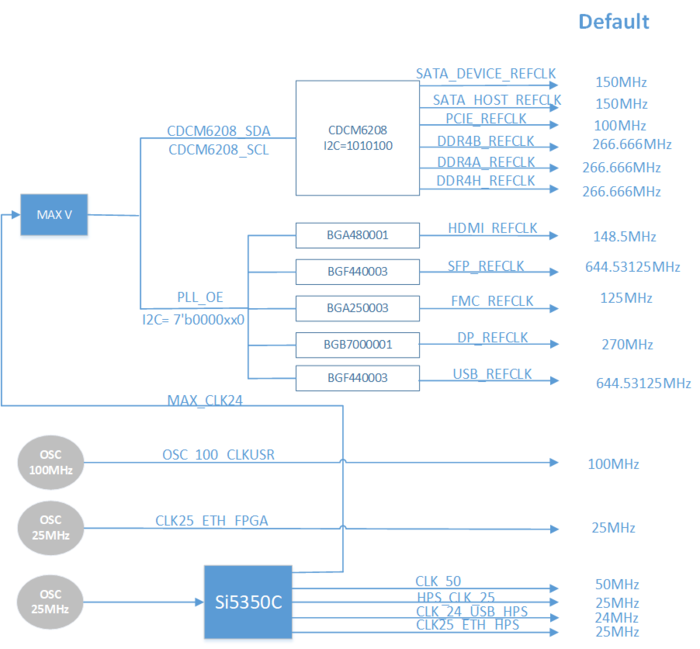

The Si5350c provides the fixed system frequencies to FPGA, HPS and other important components. There are four 50 MHz connected to the dedicated clock pins of the FPGA, which can be used by PLL for clock multiplier or frequency division. In addition, there are Programmable PLL (CDCM6280, BGA/FXXXXX) available for providing the clocks to the peripherals on the board, such as HDMI and communication interfaces. There is a default clock when power on, it also supports the users to change the frequency via I2C interface for special requirement.

- Figure 6-1 System Clock in the DE10-Advanced

- Figure 6-2 shows the default settings for different PLLs