DE10 Advance Board Setup: MSEL Settings

From Terasic Wiki

(Difference between revisions)

(→FPPx32 Mode (Default)) |

|||

| (One intermediate revision not shown) | |||

| Line 2: | Line 2: | ||

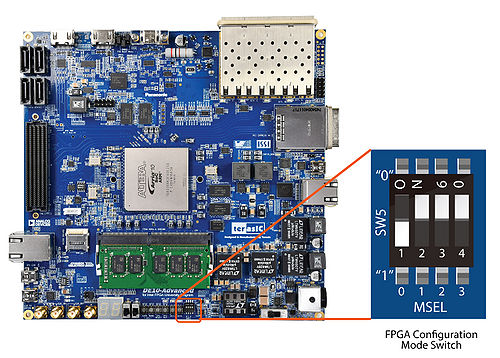

The FPGA Configuration Mode Switch (MSEL) shown in Figure 2-1 is by default set to 001 (MSEL [2:0] = 001). The setting corresponds to FPGA configured from HPS software (in the SD Card) in FPP mode. '''If users want to boot with Linux VNC desktop, please setting MSEL switch in this mode'''. | The FPGA Configuration Mode Switch (MSEL) shown in Figure 2-1 is by default set to 001 (MSEL [2:0] = 001). The setting corresponds to FPGA configured from HPS software (in the SD Card) in FPP mode. '''If users want to boot with Linux VNC desktop, please setting MSEL switch in this mode'''. | ||

| - | + | :::[[File:De10-advanced revc msel fppmode.jpg|500px]] | |

| - | ::::Figure 2-1 FPGA Configuration Mode Switch set in FPPx32 Mode | + | :::::Figure 2-1 FPGA Configuration Mode Switch set in FPPx32 Mode |

| - | + | ||

=AS Mode= | =AS Mode= | ||

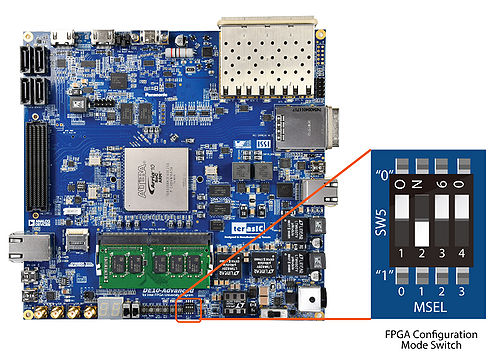

When the board is powered on and MSEL [2:0] is set to “010” (See Figure 2-2), the FPGA is configured from EPCQ. | When the board is powered on and MSEL [2:0] is set to “010” (See Figure 2-2), the FPGA is configured from EPCQ. | ||

| - | + | :::[[File:De10-advanced revc msel asmode.jpg|500px]] | |

| - | ::::Figure 2-2 FPGA Configuration Mode Switch set in AS Mode | + | ::::::Figure 2-2 FPGA Configuration Mode Switch set in AS Mode |

'''[[DE10-Advance Getting Start Guide revC#Chapter 2 Development Board Setup|Back]]''' | '''[[DE10-Advance Getting Start Guide revC#Chapter 2 Development Board Setup|Back]]''' | ||

Latest revision as of 16:08, 30 August 2018

FPPx32 Mode (Default)

The FPGA Configuration Mode Switch (MSEL) shown in Figure 2-1 is by default set to 001 (MSEL [2:0] = 001). The setting corresponds to FPGA configured from HPS software (in the SD Card) in FPP mode. If users want to boot with Linux VNC desktop, please setting MSEL switch in this mode.

AS Mode

When the board is powered on and MSEL [2:0] is set to “010” (See Figure 2-2), the FPGA is configured from EPCQ.