DE2-115 FAQ English version

From Terasic Wiki

-

- Q::What is the function of the JP4 on DE2-115?

- A:The JP4 on DE2-115 is designed and reserved for MIPS CPU; users can also use it for general FPGA IO design application.

-

- Q::What OS does the USB driver of DE2-115 support

- A:DE2-115 is equipped with two types of USB chips; they are NXP ISP1362 and Cyptess cy7c67200. The DE2-115 currently available comes with Cypress cy7c67200. The driver provided in the system CD supports windows 7 for 32 /64bit and Windows XP for 32/64bit.

-

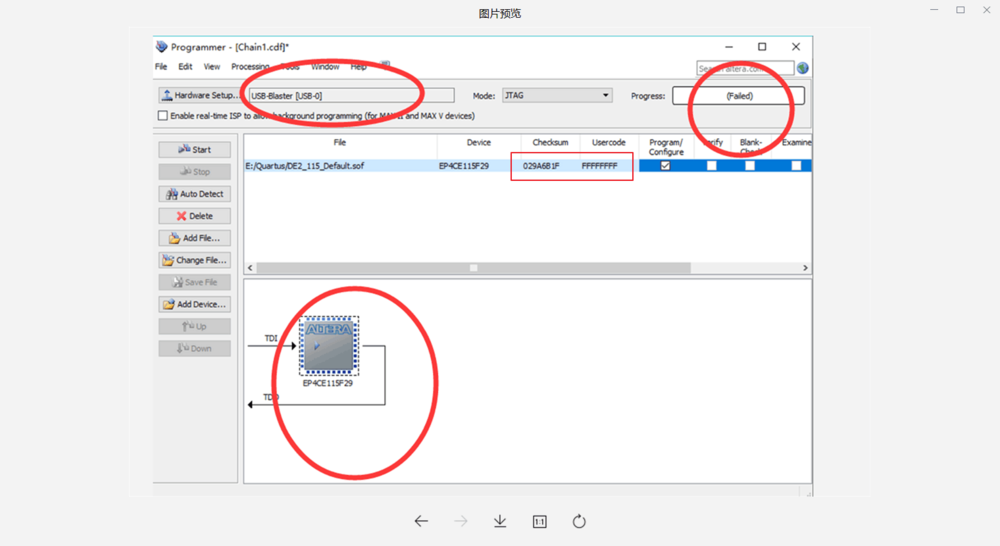

- Q::What can you do when failing to download the .sof file into the FPGA of the DE2-115 and encountering the situation as shown below??

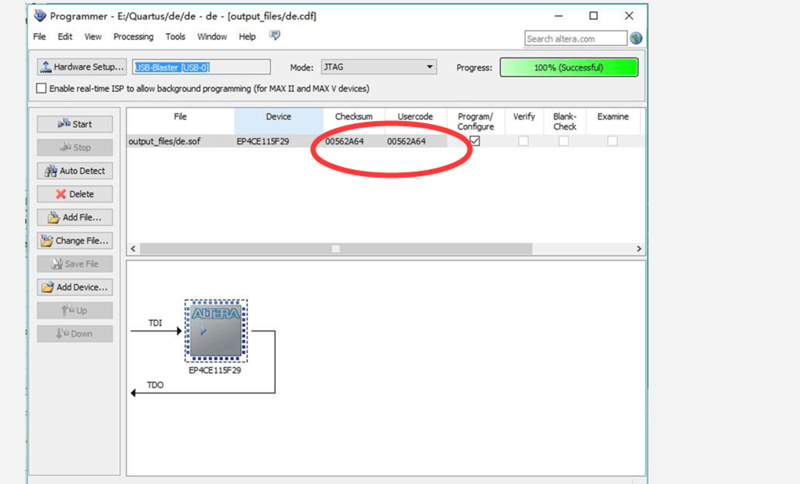

- A:Normally the checksum and usercode should be the same (as shown below). From the previous picture, we can see the USB-Blaster hardware exists, but the checksum and the usercode are different. In this situation, please make sure your JP2 jumper setting and the JTAG-Chain are correct (for more details, please refer to DE2_115_User_manual.pdf, page No. 30)..

-

- Q::How can you troubleshoot the problems first when failing to program the .sof file download into FPGA of the DE2-115?

- A:You can start with the followin:

- Check the SW19 and make sure it’s set to “RUN”

- Have a test to see if DE2-115 would run the default code when power up.

- Check the JP3 jumper setting. If DE2-115 is without any daughter cards connected, JP3 should be shorted to 1&2 connectors; while if the JTAG signal needs to be connected to the daughter card, JP3 should then be shorted to 2&3 connectors.

- Open the Quartus Programmer window and click on the "Hardware Setup." button to see if there is a USB Blaster hardware shows up; then click "Auto Detect" to see if the Quartus software reports an error.

-

- Q::What is the maximum transmission rate (MB/s) for the DE2-115 network interface?

- A:The projects provided on Terasic official web are made based on Nios by using Altera’s TSE IP. We’ve got a result which is approximately 100~200 Mb/s at the application level. Users can also design or optimize their own projects to speed up the transmission.