Documents

| 標題 | 版本 | 大小 | 日期 | 下載 |

|---|---|---|---|---|

| DE10-Lite User Manual | 1.6 | 3,925(KB) | 2020-06-05 |

Daughter Card Demonstrations

| 標題 | 版本 | 大小 | 日期 | 下載 |

|---|---|---|---|---|

| D8M-GPIO | 2019-05-24 | |||

| LT24 | 2016-09-19 | |||

| MTL2 | 2016-09-19 |

CD-ROM

| 標題 | 版本 | 大小 | 日期 | 下載 |

|---|---|---|---|---|

| DE10-Lite CD-ROM | 2.2.0 | 2025-04-01 | ||

| ControlPanel | 1.0.3 | 2018-05-10 | ||

| Quartus Download | 15.1.2 | 2016-06-21 |

3D-Printer-Case

| 標題 | 版本 | 大小 | 日期 | 下載 |

|---|---|---|---|---|

| Top cover | 106(KB) | 2016-08-18 | ||

| Bottom cover | 33(KB) | 2016-08-18 |

友晶創新所發表之範例程式碼,基於免費分享之原則,不提供任何形式的講解或修改。如需進一步範例程式碼講解或修改的協助,我們將轉至「設計服務部門」評估。

本授權條款允許使用者於使用所有友晶及 Intel 開發板時,得以重製、散布、傳輸以及修改友晶創新提供的原始碼,但不得為商業目的之使用。使用時必須於引用處表彰友晶創新 (Terasic Inc.) 之商號。

系統 CD 中的示例

- Factory Default Code

- SDRAM Test in Nios II

- SDRAM Test in Verilog

- VGA Pattern

- Accelerometer Level

- Accelerometer Rock

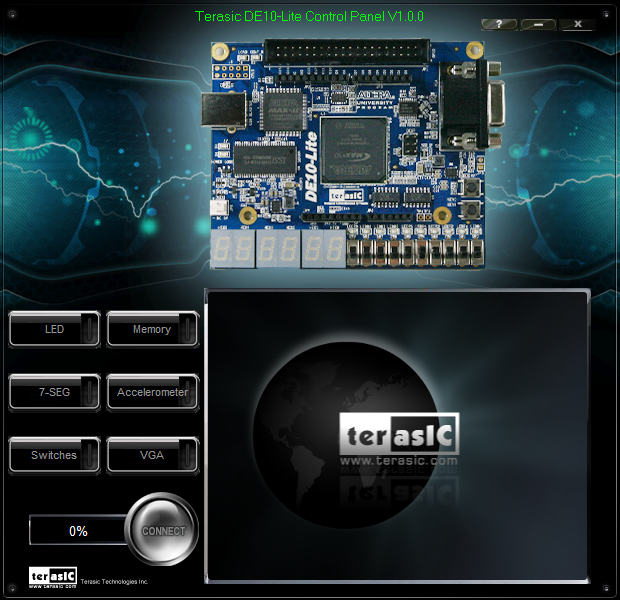

DE10-Lite 控制面板

允許用戶從主機訪問 DE10-Lite 開發板上的各種組件

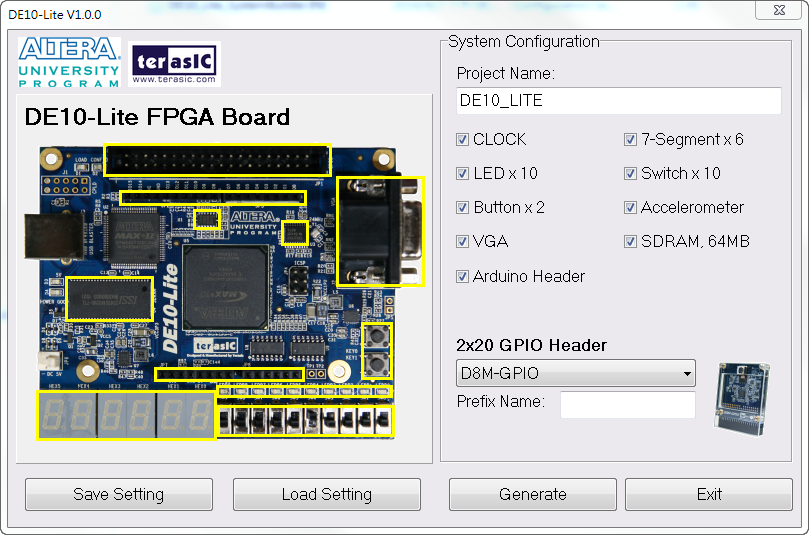

DE10-Lite System Builder

此工具允許用戶在 DE10-Lite 開發板上創建自定義設計的 Quartus 工程,並自動生成頂層設計文件、管腳分配和 I/O 標準設置。

其他您可能感興趣的設計資源:

學校:康奈爾大學高級講師——Bruce Land