Word2wiki bal gsq

From Terasic Wiki

=

Contents |

Chpater1 Chapter 7PCI Express Design for Windows =

1-0-1 7.1 PCI Express System Infrastructure

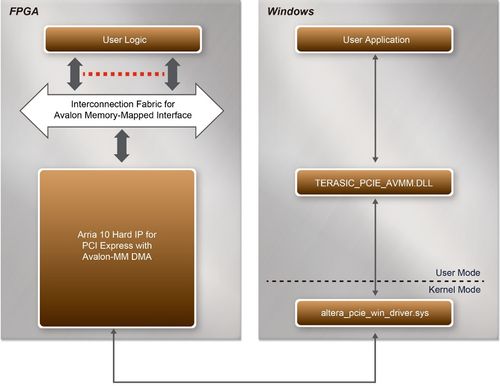

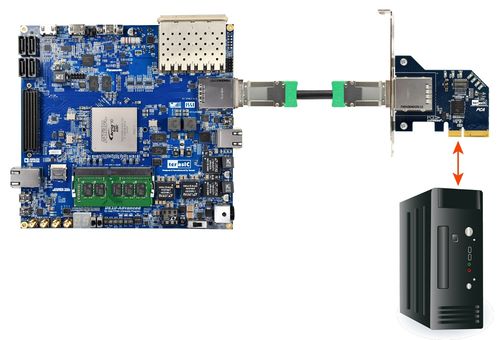

Figure 7-1 shows the infrastructure of the PCI Express System in this demonstration. It consists of two primary components: FPGA System and PC System. The FPGA System is developed based on Arria 10 Hard IP for PCI Express with Avalon-MM DMA. The application software on the PC side is developed by Terasic based on Altera’s PCIe kernel mode driver.

1-0-2 7.2 PC PCI Express Software SDK

- PCI Express Library

- PCI Express Examples

- Data read and write by DMA

1-0-3 7.3 PCI Express Software Stack

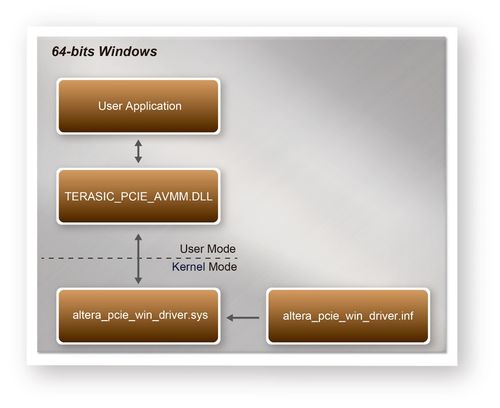

Figure 7-2 shows the software stack for the PCI Express application software on 64-bit Windows. The PCIe library module TERASIC_PCIE_AVMM.dll provides DMA and direct I/O access for user application program to communicate with FPGA. Users can develop their applications based on this DLL. The altera_pcie_win_driver.sys kernel driver is provided by Altera.

- Altera_pcie_win_driver.inf

- Altera_pcie_win_driver.sys

- WdfCoinstaller01011.dll

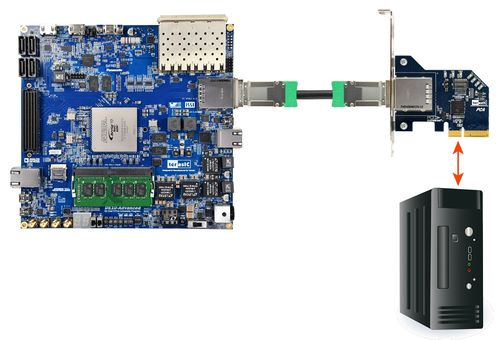

- Plug the PCIe adapter card into the PCIe slot on the PC motherboard. Use the PCIe cable to connect to the DE10-Advanced PCIE connector and the PCIe adapter card (See Figure 7-3)

- Make sure Altera Programmer and USB-Blaster II driver are installed

- Execute test.bat in "CDROM\Demonstrations\PCIe_Fundamental\demo_batch" to configure the FPGA

- Restart windows operation system

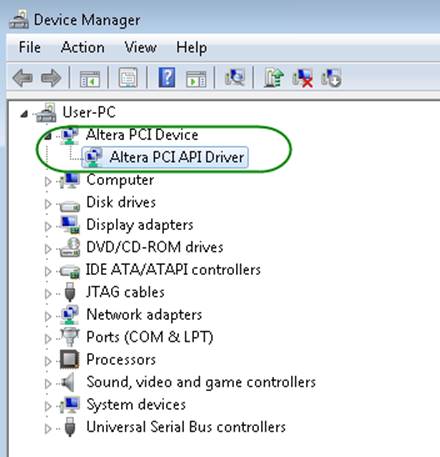

- Click Control Panel menu from Windows Start menu. Click Hardware and Sound item before clicking the Device Manager to launch the Device Manager dialog. There will be a PCI Device item in the dialog, as shown in Figure 7-4. Move the mouse cursor to the PCI Device item and right click it to select the Update Driver Software... item.

- Create a Software Application

- TERASIC_PCIE_AVMM.dll (64-bit dll)

- Include TERASIC_PCIE_AVMM.h in the C/C++ project.

- Copy TERASIC_PCIE_AVMM.dll to the folder where the project.exe is located.

- Dynamically load TERASIC_PCIE_AVMM.dll in C/C++ program. To load the dll, please refer to the PCIe fundamental example below.

- Call the SDK API to implement the desired application.

1-0-4 7.4 PCI Express Library API

| Function:

Open a specified PCIe card with vendor ID, device ID, and matched card index. |

| Prototype:

PCIE_HANDLE PCIE_Open( uint8_t wVendorID, uint8_t wDeviceID, uint8_t wCardIndex); |

| Parameters:

wVendorID: Specify the desired vendor ID. A zero value means to ignore the vendor ID. wDeviceID: Specify the desired device ID. A zero value means to ignore the device ID. wCardIndex: Specify the matched card index, a zero based index, based on the matched vendor ID and device ID. |

| Return Value:

Return a handle to presents specified PCIe card. A positive value is return if the PCIe card is opened successfully. A value zero means failed to connect the target PCIe card. This handle value is used as a parameter for other functions, e.g. PCIE_Read32. Users need to call PCIE_Close to release handle once the handle is no more used. |

| Function:

Close a handle associated to the PCIe card. |

| Prototype:

void PCIE_Close( PCIE_HANDLE hPCIE); |

| Parameters:

hPCIE: A PCIe handle return by PCIE_Open function. |

| Return Value:

None. |

| Function:

Read a 32-bit data from the FPGA board. |

| Prototype:

bool PCIE_Read32( PCIE_HANDLE hPCIE, PCIE_BAR PcieBar, PCIE_ADDRESS PcieAddress, uint32_t *pdwData); |

| Parameters:

hPCIE: A PCIe handle return by PCIE_Open function. PcieBar: Specify the target BAR. PcieAddress: Specify the target address in FPGA. pdwData: A buffer to retrieve the 32-bit data. |

| Return Value:

Return true if read data is successful; otherwise false is returned. |

| Function:

Write a 32-bit data to the FPGA Board. |

| Prototype:

bool PCIE_Write32( PCIE_HANDLE hPCIE, PCIE_BAR PcieBar, PCIE_ADDRESS PcieAddress, uint32_t dwData); |

| Parameters:

hPCIE: A PCIe handle return by PCIE_Open function. PcieBar: Specify the target BAR. PcieAddress: Specify the target address in FPGA. dwData: Specify a 32-bit data which will be written to FPGA board. |

| Return Value:

Return true if write data is successful; otherwise false is returned. |

| Function:

Read an 8-bit data from the FPGA board. |

| Prototype:

bool PCIE_Read8( PCIE_HANDLE hPCIE, PCIE_BAR PcieBar, PCIE_ADDRESS PcieAddress, uint8_t *pByte); |

| Parameters:

hPCIE: A PCIe handle return by PCIE_Open function. PcieBar: Specify the target BAR. PcieAddress: Specify the target address in FPGA. pByte: A buffer to retrieve the 8-bit data. |

| Return Value:

Return true if read data is successful; otherwise false is returned. |

| Function:

Write an 8-bit data to the FPGA Board. |

| Prototype:

bool PCIE_Write8( PCIE_HANDLE hPCIE, PCIE_BAR PcieBar, PCIE_ADDRESS PcieAddress, uint8_t Byte); |

| Parameters:

hPCIE: A PCIe handle return by PCIE_Open function. PcieBar: Specify the target BAR. PcieAddress: Specify the target address in FPGA. Byte: Specify an 8-bit data which will be written to FPGA board. |

| Return Value:

Return true if write data is successful; otherwise false is returned. |

| Function:

Read data from the memory-mapped memory of FPGA board in DMA. Maximal read size is (4GB-1) bytes. |

| Prototype:

bool PCIE_DmaRead( PCIE_HANDLE hPCIE, PCIE_LOCAL_ADDRESS LocalAddress, void *pBuffer, uint32_t dwBufSize ); |

| Parameters:

hPCIE: A PCIe handle return by PCIE_Open function. LocalAddress: Specify the target memory-mapped address in FPGA. pBuffer: A pointer to a memory buffer to retrieved the data from FPGA. The size of buffer should be equal or larger the dwBufSize. dwBufSize: Specify the byte number of data retrieved from FPGA. |

| Return Value:

Return true if read data is successful; otherwise false is returned. |

| Function:

Write data to the memory-mapped memory of FPGA board in DMA. |

| Prototype:

bool PCIE_DmaWrite( PCIE_HANDLE hPCIE, PCIE_LOCAL_ADDRESS LocalAddress, void *pData, uint32_t dwDataSize ); |

| Parameters:

hPCIE: A PCIe handle return by PCIE_Open function. LocalAddress: Specify the target memory mapped address in FPGA. pData: A pointer to a memory buffer to store the data which will be written to FPGA. dwDataSize: Specify the byte number of data which will be written to FPGA. |

| Return Value:

Return true if write data is successful; otherwise false is returned. |

- PCIE_ConfigRead32

| Function:

Read PCIe Configuration Table. Read a 32-bit data by given a byte offset. |

| Prototype:

bool PCIE_ConfigRead32 ( PCIE_HANDLE hPCIE, uint32_t Offset, uint32_t *pdwData ); |

| Parameters:

hPCIE: A PCIe handle return by PCIE_Open function. Offset: Specify the target byte of offset in PCIe configuration table. pdwData: A 4-bytes buffer to retrieve the 32-bit data. |

| Return Value:

Return true if read data is successful; otherwise false is returned.

|

1-0-5 7.5 PCIe Reference Design - Fundamental

- Download Batch file: test.bat

- Windows Application Software folder : windows_app, includes

- PCIE_FUNDAMENTAL.exe

- TERASIC_PCIE_AVMM.DLL

- Install the FPGA board on your PC as shown in Figure 7-3.

- Configure FPGA with PCIe_Fundamental.sof by executing the test.bat.

- Install PCIe driver if necessary. The driver is located in the folder:

- Make sure the Windows has detected the FPGA Board by checking the Windows Control panel as shown in Figure 7-10.

- Development Tools

- Quartus Prime 18.0 Standard Edition

- Visual C++ 2012

- Demonstration Source Code Location

- Quartus Project: Demonstrations\PCIe_Fundamental

- C++ Project: Demonstrations\PCIe_SW_KIT\Windows\PCIE_FUNDAMENTAL

- FPGA Application Design

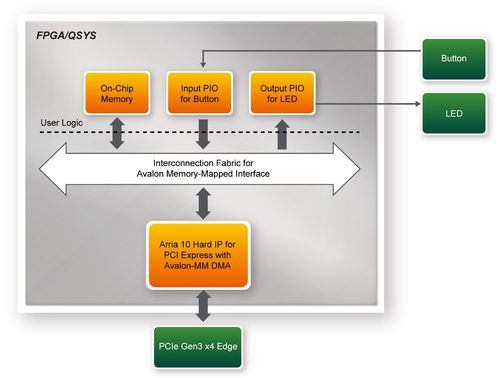

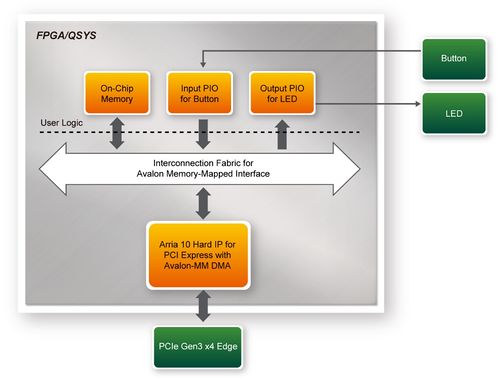

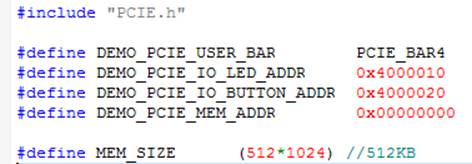

Figure 7-15 shows the system block diagram in the FPGA system. In the Qsys, Altera PIO controller is used to control the LED and monitor the Button Status, and the On-Chip memory is used for performing DMA testing. The PIO controllers and the On-Chip memory are connected to the PCI Express Hard IP controller through the Memory-Mapped Interface.

| Name | Description |

| PCIE_FUNDAMENTAL.cpp | Main program |

| PCIE.c | Implement dynamically load for TERAISC_PCIE_AVMM.DLL |

| PCIE.h | |

| TERASIC_PCIE_AVMM.h | SDK library file, defines constant and data structure |

- The PCI express driver is loaded successfully.

| 500px |

| 500px |

1-0-6 7.6 PCIe Reference Design - DDR4

- Download Batch file: test.bat

- Windows Application Software folder : windows_app, includes

- PCIE_DDR4.exe

- TERASIC_PCIE_AVMM.dll

- Install DDR4 2400 4GB SODIMM on the FPGA board.

- Install the FPGA board on your PC as shown in Figure 7-3.

- Configure FPGA with PCIe_DDR4.sof by executing the test.bat.

- Install PCIe driver if necessary.

- Restart Windows

- Make sure the Windows has detected the FPGA Board by checking the Windows Control panel.

- Goto windows_app folder, execute PCIE_DDR4.exe. A menu will appear as shown in Figure 7-16.

- Quartus Prime 18.0 Standard Edition

- Visual C++ 2012

- Demonstration Source Code Location

- Quartus Project: Demonstrations\PCIE_DDR4

- Visual C++ Project: Demonstrations\PCIe_SW_KIT\Windows\PCIe_DDR4

- FPGA Application Design

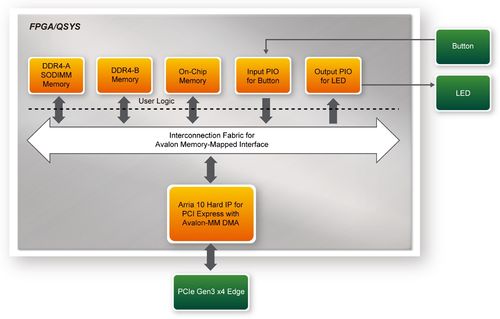

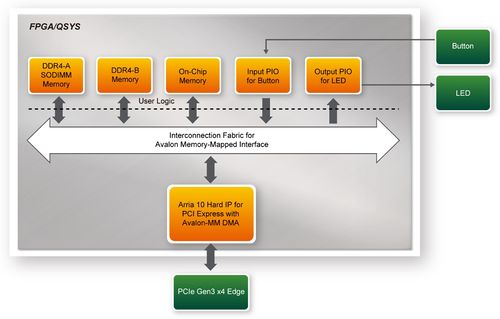

Figure 7-21 shows the system block diagram in the FPGA system. In the Qsys, Altera PIO controller is used to control the LED and monitor the Button Status, and the On-Chip memory is used for performing DMA testing. The PIO controllers and the On-Chip memory are connected to the PCI Express Hard IP controller through the Memory-Mapped Interface.

| Name | Description |

| PCIE_DDR4.cpp | Main program |

| PCIE.c | Implement dynamically load for TERAISC_PCIE_AVMM.DLL |

| PCIE.h | |

| TERASIC_PCIE_AVMM.h | SDK library file, defines constant and data structure |

- The PCI express driver is loaded successfully.

| 500px |

| 500px |

The PCIe link information is implemented by PCIE_ConfigRead32 API, as shown below:

=

Chapter 8Chpater2 PCI Express Reference Design for Linux =

2-0-7 8.1 PCI Express System Infrastructure

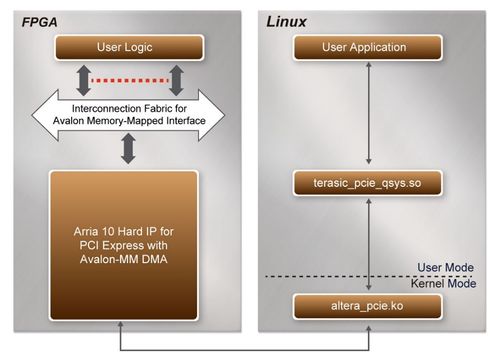

Figure 8-1 shows the infrastructure of the PCI Express System in this demonstration. It consists of two primary components: FPGA System and PC System. The FPGA System is developed based on Arria 10 Hard IP for PCI Express with Avalon-MM DMA. The application software on the PC side is developed by Terasic based on Altera’s PCIe kernel mode driver.

2-0-8 8.2 PC PCI Express Software SDK

- PCI Express Library

- PCI Express Examples

- Data read and write by DMA

2-0-9 8.3 PCI Express Software Stack

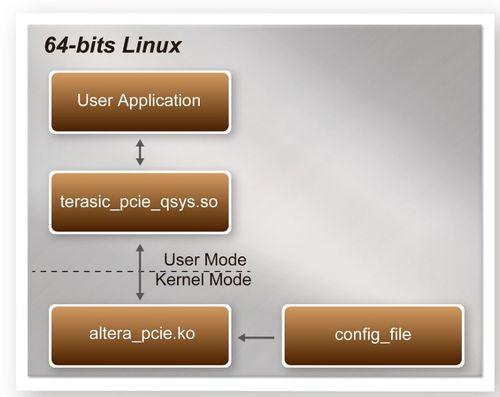

Figure 8-2 shows the software stack for the PCI Express application software on 64-bit Linux. The PCIe library module terasic_pcie_qys.so provides DMA and direct I/O access for user application program to communicate with FPGA. Users can develop their applications based on this .so library file. The altera_pcie.ko kernel driver is provided by Altera.

The folder includes the following files:* altera_pcie.c

- altera_pcie.h

- altera_pcie_cmd.h

- Makefile

- load_driver

- unload

- config_file

- Make sure the DE10-Advanced and the PC are both powered off.

- Plug the PCIe adapter card into the PCIe slot on the PC motherboard. Use the PCIe cable to connect to the DE10-Advanced PCIE connector and the PCIe adapter card (See Figure 8-3)

- Open a terminal and use "cd" command to goto the folder"CDROM/Demonstrations/PCIe_Fundamental/demo_batch".

- Set QUARTUS_ROOTDIR variable pointing to the Quartus installation path. Set QUARTUS_ROOTDIR variable by tying the following commands in terminal. Replace “/home/centos/intelFPGA/18.0/quartus” to your quartus installation path.

| export QUARTUS_ROOTDIR=/home/centos/intelFPGA/18.0/quartus |

- Execute "sudo -E sh test.sh" command to configure the FPGA

- Restart Linux operation system. In Linux, open a terminal and use “cd” command to goto the PCIe_Driver folder

- Type the following commands to compile and install the driver altera_pcie.ko, and make sure driver is loaded successfully and FPGA is detected by the driver as shown in Figure 8-4.

- make

- sudo sh load_driver

- dmesg | tail -n 15

- terasic_pcie_qsys.so (64-bit library)

- Include TERASIC_PCIE_AVMM.h in the C/C++ project.

- Copy terasic_pcie_qsys.so to the folder where the project execution file is located.

- Dynamically load terasic_pcie_qsys.so in C/C++ program. To load the terasic_pcie_qsys.so, please refer to the PCIe fundamental example below.

- Call the library API to implement the desired application.

2-0-10 8.4 PCI Express Library API

2-0-11 8.5 PCIe Reference Design – Fundamental

- Download Batch file: test.sh

- Linux Application Software folder : linux_app, includes

- PCIE_FUNDAMENTAL

- terasic_pcie_qsys.so

- Demonstration Setup

- Install the FPGA board on your PC as shown in Figure8-3.

- Open a terminal and use "cd" command to goto "CDROM/Demonstrations/PCIe_Fundamental/demo_batch".

- Set QUARTUS_ROOTDIR variable pointing to the Quartus installation path. Set QUARTUS_ROOTDIR variable by tying the following commands in terminal. Replace /home/centos/intelFPGA/18.0/quartus to your quartus installation path.

| export QUARTUS_ROOTDIR=/home/centos/intelFPGA/18.0/quartus |

- Execute "sudo -E sh test.sh" command to configure the FPGA

- Restart Linux

- Install PCIe driver. The driver is located in the folder:

- Development Tools

- Quartus Prime 18.0 Standard Edition

- GNU Compiler Collection, Version 4.8 is recommend

- Demonstration Source Code Location

- Quartus Project: Demonstrations/PCIe_Fundamental

- C++ Project: Demonstrations/PCIe_SW_KIT/Linux/PCIE_FUNDAMENTAL

- FPGA Application Design

Figure 8-9 shows the system block diagram in the FPGA system. In the Qsys, Altera PIO controller is used to control the LED and monitor the Button Status, and the On-Chip memory is used for performing DMA testing. The PIO controllers and the On-Chip memory are connected to the PCI Express Hard IP controller through the Memory-Mapped Interface.

| Name | Description |

| PCIE_FUNDAMENTAL.cpp | Main program |

| PCIE.c | Implement dynamically load for terasic_pcie_qsys.so library file |

| PCIE.h | |

| TERASIC_PCIE_AVMM.h | SDK library file, defines constant and data structure |

- The PCI express driver is loaded successfully.

|

| |

2-0-12 8.5 PCIe Reference Design - DDR4

- Download Batch file: test.sh

- Linux Application Software folder : linux_app, includes

- PCIE_DDR4

- terasic_pcie_qsys.so

- Demonstration Setup

- Install DDR4 2400 4GB SODIMM on the FPGA board.

- Install the FPGA board on your PC as shown in Figure8-3.

- Open a terminal and use "cd" command to goto "CDROM/Demonstrations/PCIe_Fundamental/demo_batch".

- Set QUARTUS_ROOTDIR variable pointing to the Quartus installation path. Set QUARTUS_ROOTDIR variable by tying the following commands in terminal. Replace /home/centos/intelFPGA/18.0/quartus to your quartus installation path.

| export QUARTUS_ROOTDIR=/home/centos/intelFPGA/18.0/quartus |

- Execute "sudo -E sh test.sh" command to configure the FPGA

- Restart Linux

- Install PCIe driver.

- Make sure the Linux has detected the FPGA Board.

- Goto linux_app folder, execute PCIE_DDR4. A menu will appear as shown in Figure 8-10.

- Development Tools

- Quartus Prime 18.0 Standard Edition

- GNU Compiler Collection, Version 4.8 is recommended

- Demonstration Source Code Location

- Quartus Project: Demonstrations/PCIE_DDR4

- C++ Project: Demonstrations/PCIe_SW_KIT/Linux/PCIe_DDR4

- FPGA Application Design

| Name | Description |

| PCIE_DDR4.cpp | Main program |

| PCIE.c | Implement dynamically load for terasic_pcie_qsys.so library file |

| PCIE.h | |

| TERASIC_PCIE_AVMM.h | SDK library file, defines constant and data structure |

- The PCI express driver is loaded successfully.

| 500px |

| |