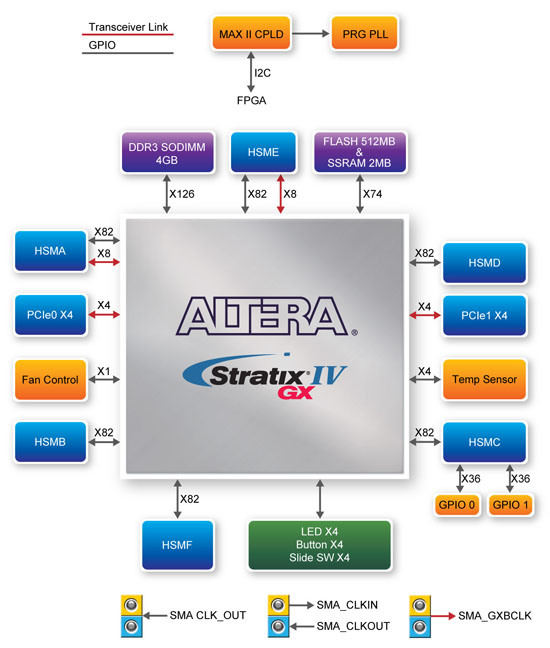

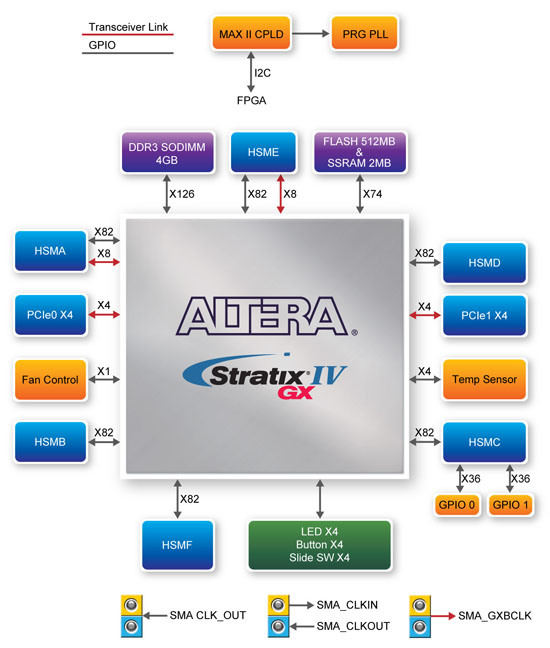

Terasic TR4 FPGA Development Kit

FPGA 器件

Stratix IV GX EP4SGX230

- 228K 逻辑单元

- 17,133 Kb 总内存

- 1,288 个 18x18 bit 乘法器

- 2 PCIE 硬核 IP

- 744 个用户 I/O

- 8 个 PLL

Stratix IV GX EP4SGX530

- 531,200 逻辑单元

- 27,376 Kb 总内存

- 1,024 个 18x18-bit 乘法器

- 4 PCIE 硬核 IP

- 744 个 用户 I/O

- 8 个 PLL

FPGA 配置

- MAXII CPLD EPM2210 系统控制器和 FPP 配置

- 板载 USB Blaster 电路用于下载程序等

- 可编程 PLL 定时芯片,通过 MAX II CPLD 配置

- 支持 JTAG 模式

Memory 器件

- 64MB 16 位数据总线

- 2MB SSRAM (512K x 32)

DDR3 SO-DIMM 接口

- 容量高达 8GB

- 最大 Memory 时钟率是 533MHz

- 理论带宽高达 68Gbps

按钮,开关,LED 灯

- 4 个用户可控 LED 灯

- 4 个用户按钮

- 4 个拨动开关

板载时钟

SMA 连接头

- SMA 接头用于差分时钟输入

- SMA 接头用于差分时钟输出

- SMA接头用于时钟输出

- SMA 接头用于外部时钟接入

2 个 PCIE x4 连接器

- 支持连接 Gen 1 2.5Gbps/lane 到 Gen2 5.0 Gbps/lane

- 高速收发器通道高达 6.5 Gbps

- 支持 Downstream 模式

6 个 172-pin HSMC

- 6 个 HSMC 连接器

- I/O 标准可配置 - 1.5V, 1.8V, 2.5V, 3.0V

- 总共 16 个高速收发器速度可达 6.5 Gbps

- HSMC A 口和 D 口总共有 55 个 true LVDS TX 通道速度达到1.6Gbps 和 17 个 Emulated LVDS TX 通道速度达到 1.1Gbps

2 个 40-pin 的 GPIO 扩展槽

- 72-pin FPGA I/O;4-pin 电源与地

- I/O 标准可配置 - 1.5V, 1.8V, 2.5V, 3.0V

- 与 HSMC pin 共用

电源

功能方塊圖