Download

Documents

| 标题 | 版本 | 大小 | 日期 | 下载 |

|---|---|---|---|---|

| TR4 User Manual | 2.1 | 11,221(KB) | 2021-01-26 | |

| Using the Design Security Feature in TR4 | 1.0 | 1,603(KB) | 2014-06-06 |

Daughter Card Demonstrations

CD-ROM

| 标题 | 版本 | 大小 | 日期 | 下载 |

|---|---|---|---|---|

| TR4 CD-ROM | 1.2.1 | 2022-07-19 | ||

| TR4 System Builder | 1.1.0 | 2017-02-06 |

友晶科技所发表之范例程式码,基於免费分享之原则,不提供任何形式的讲解或修改。如需进一步范例程式码讲解或修改的协助,我们将转至 "设计服务部门" 评估。

本授权条款允许使用者於使用所有友晶及 Intel 开发板时,得以重制、散布、传输以及修改友晶科技提供的源码,但不得为商业目的之使用。使用时必须於引用处表彰友晶科技 (Terasic Inc.) 之商号。

Download Intel® Quartus® Prime Software

The TR4 requires Quartus II Standard Edition Software to support the Stratix IV GX device.

Please contact us for download information: support@terasic.com

TR4 Tools 部分

TR4 Control Panel – 允许用户从主机访问 TR4 开发板上的各种组件。

TR4 Control Panel

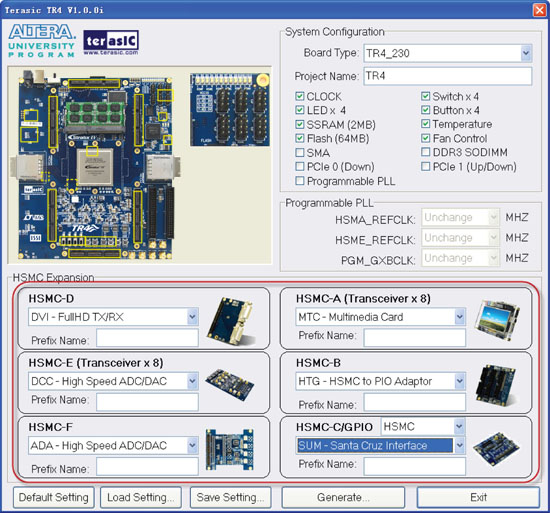

TR4 System Builder – 为TR4 提供的强大设计工具。这个工具将允许用户根据自己的设计,定制一个Quartus II工程文件。TR4 System Builder将自动生成TR4开发板的顶层设计文件、引脚分配和I/O标准设置。此外,通过HSMC接口,您可以使用TR4 System Builder与TR4一起选择各种子卡。

TR4 System Builder

自动生成如下 Quartus II 工程文件:

- Quartus II Project File (.qpf)

- Quartus II Setting File (.qsf)

- Top-Level Design File (.v)

- External PLL Contorller (.v)

- Synopsis Design Constraints file (.sdc)

- Pin Assignment Document (.htm)

TR4 参考设计

- LEDs呼吸灯设计

- 外部时钟发生器

- High Speed Mezzanine Card 回环测试

- 基于Nios II 设计的DDR3 读/写 测试

- 基于HDL 设计的DDR3 读/写 测试