友晶受邀於2020年11月在亞東技術學院電子工程系舉辦 RISC-V on T-Core 培訓課程,該課程以友晶設計製造之 T-Core 平臺分別從理論上對 RISC-V 架構進行深入淺出的分析輔以現場實作,同學們皆踴躍參與。

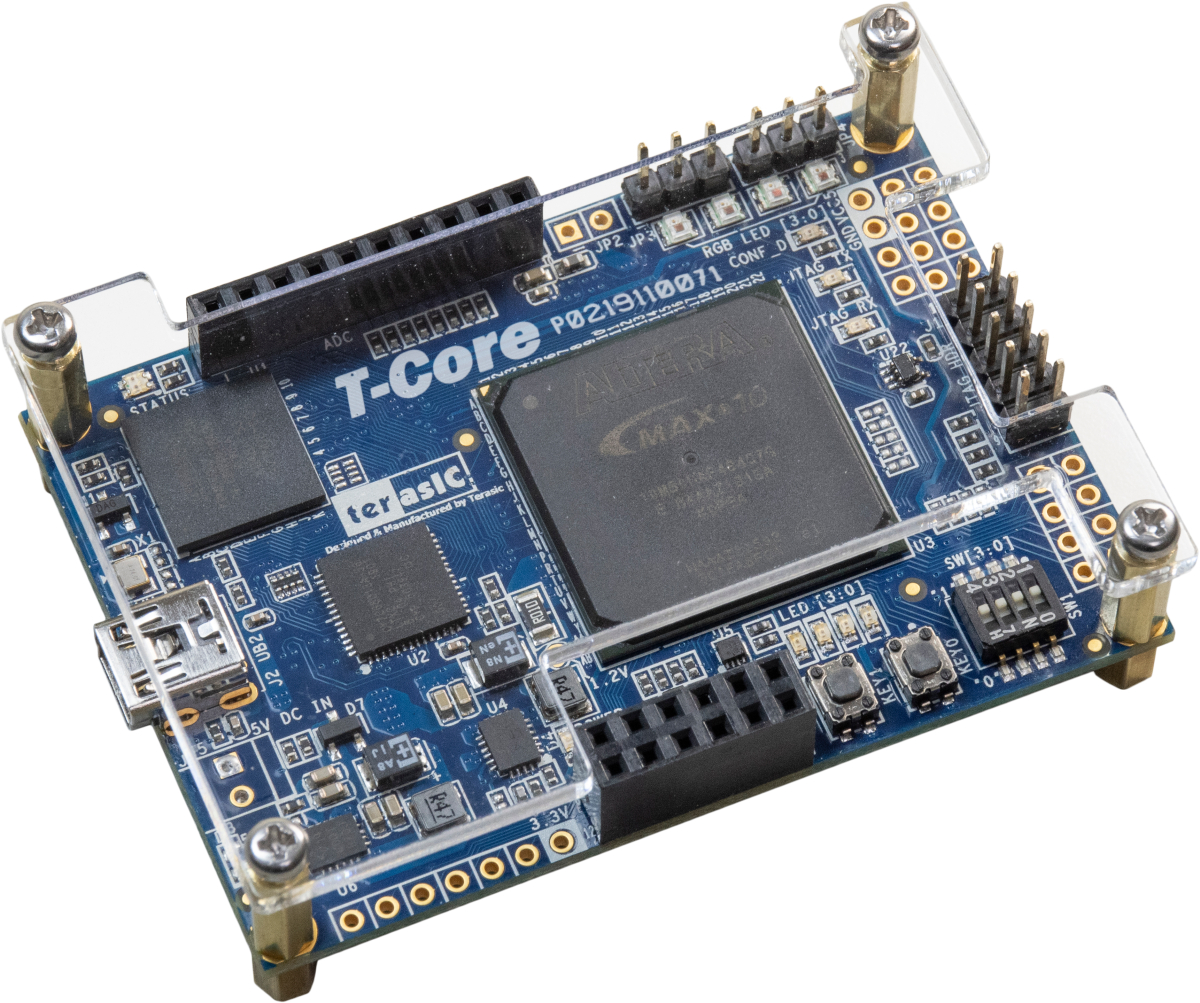

亞東技術學院電子工程系為因應世界之發展趨勢,對於提供學生最先進優良的軟硬體資源不遺餘力。系上已成立由Intel FPGA 大學計畫支持、友晶共同揭牌的「SoCFPGA & OpenCL 聯合實驗室」特色實驗室多年,並也規劃特色研究領域。電子工程系陳韋達教授看準了 RISC-V 的未來趨勢及其廣泛應用,希望藉由友晶帶來的RISC-V on T-Core 札實授課內容及實作課程,搭配友晶資深研發工程師現場親自指導,讓學員們都能輕易地上手。學員於課後紛紛表示,授課的內容相當紮實,講師對實作步驟皆細心解說,雖僅有三個小時的培訓課程,卻是受益良多。亞東技術學院更已購進數十套的 T-Core 開發板供學生們使用,讓學生們得以將於課程中埋下的種子在平台上繼續扎根,藉以大幅提升莘莘學子們 FPGA 的應用能力。

友晶也將一系列的RISC-V on T-Core 以線上方式呈現,完整課程內容請見下方連結。

授課實況

學員們認真實作

RISC-V on T-Core 免費線上課程

RISC-V 是一個基於精簡指令集(RISC)原則的開源指令集架構(ISA),是一種免費開放的指令集。具有極強的擴展性,易於移植、模組化設計、完整的工具鏈等特點。

點擊訂閱Terasic電子報 ,輕鬆獲取第一手消息!