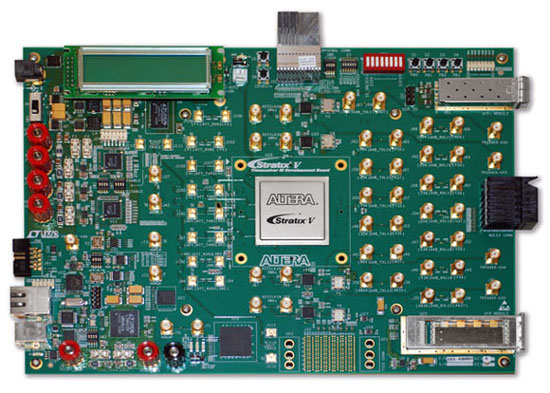

The Altera® Stratix® V GT Transceiver Signal Integrity (SI) Development Kit provides a platform for electrical compliance testing and interoperability analysis. The accessibility to multiple channels allows for real-world analysis as implemented in the system with transceiver channels available through SMA and popular backplane connectors. You can use this development kit to perform the following tasks:

- Evaluate transceiver link performance up to 28 Gbps

- Generate and check pseudo-random binary sequence (PRBS) patterns via a simple to use GUI (does not require the Quartus® II software)

- Access advanced equalization to fine tune link settings for optimal bit error ratio (BER)

- Perform jitter analysis

- Verify physical media attachment (PMA) interoperability with Stratix V GT FPGAs for targeted protocols, such as CEI-25/28G, CEI-11G, PCI Express® (PCIe®) Gen 3.0, 10GBASE-KR, 10 Gigabit Ethernet, XAUI, CEI-6G, Serial RapidIO® , HD-SDI, and others

- Use the built-in high speed backplane connectors to evaluate custom backplane performance and evaluate link BER