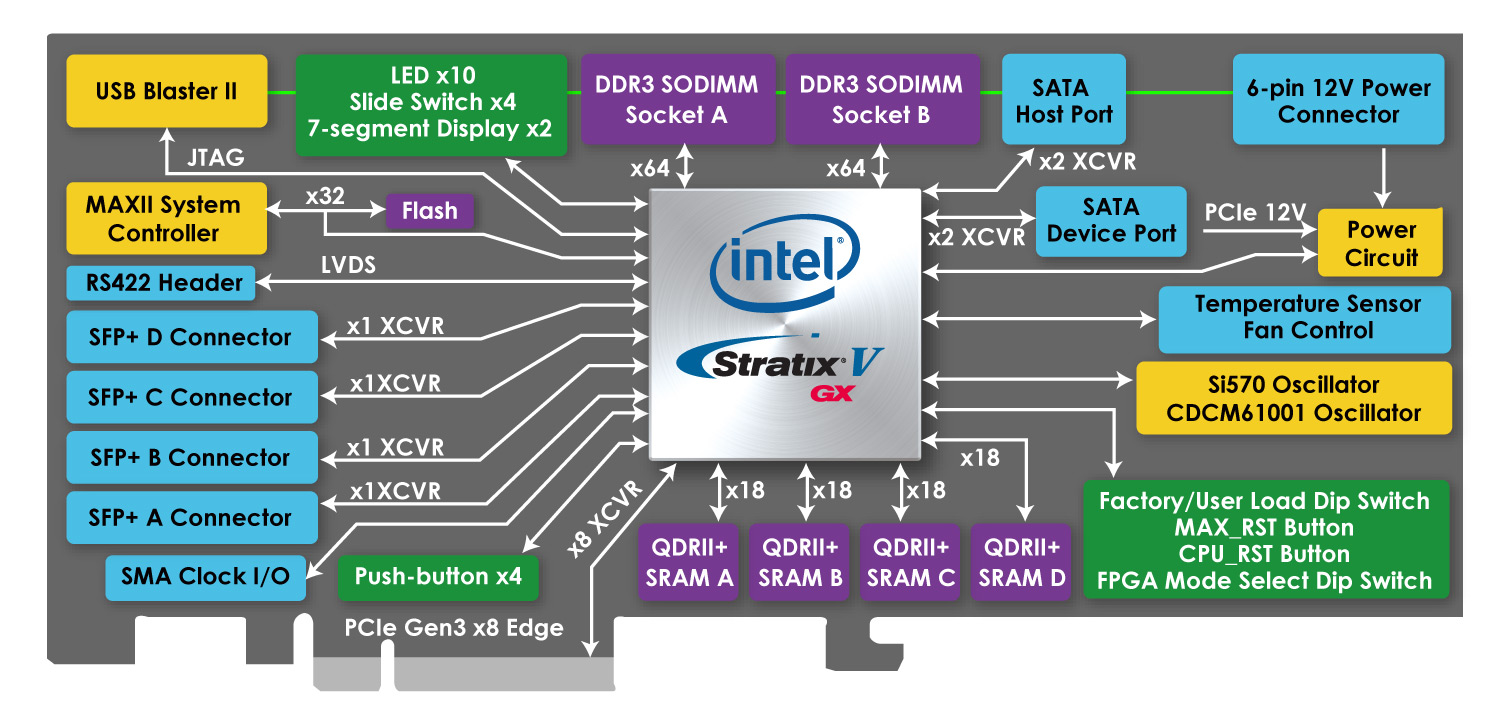

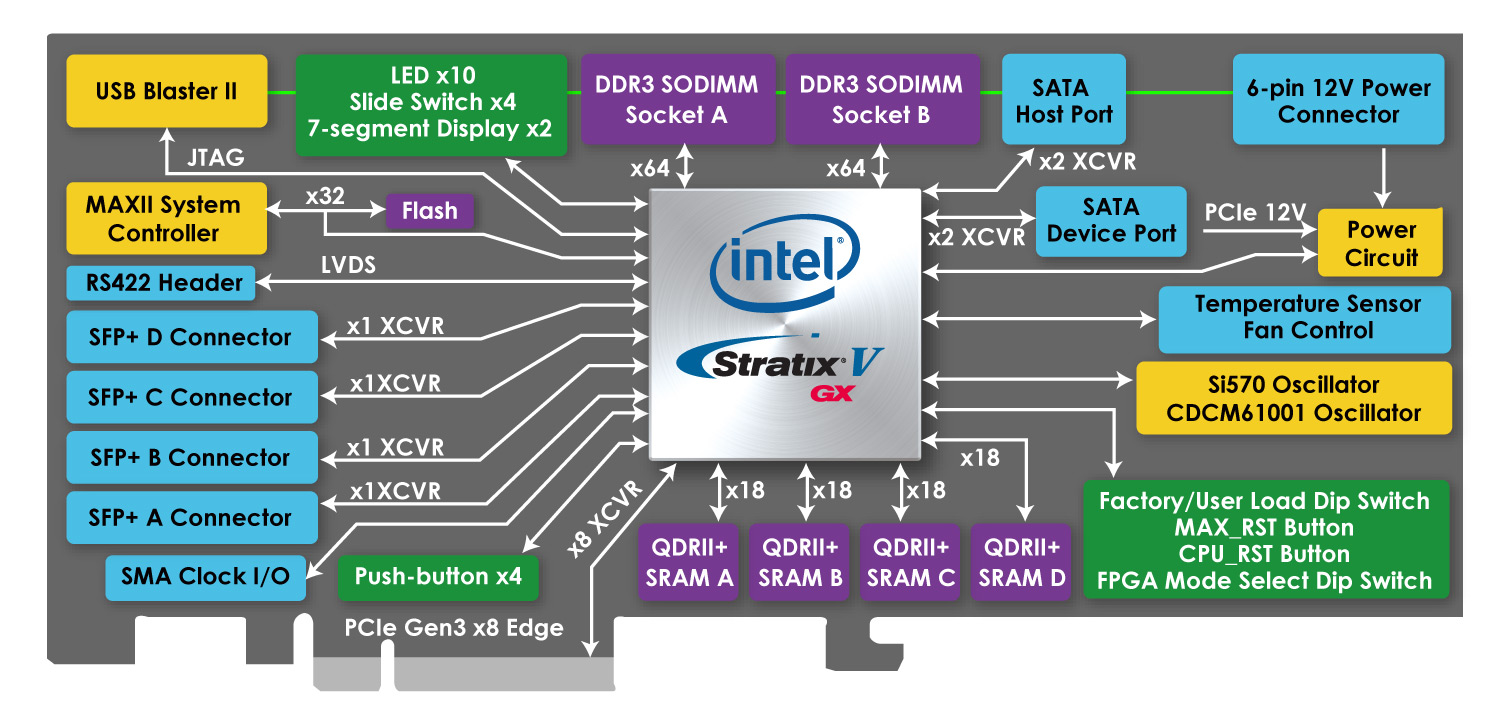

DE5-Net Development and Education Kit

FPGA

FPGA

- Altera Stratix®

V GX FPGA (5SGXEA7N2F45C2)

FPGA Configuration

- On-Board USB Blaster II or JTAG header for FPGA programming Fast passive parallel (FPPx32)

- configuration via MAX II CPLD and flash memory

Memory

Memory

- Two Independent DDR3 SODIMM Socket, Up to 8GB 800 MHz or 4GB 933 MHz for each socket

- FPGA Configuration

- Four Independent 550MHz SRAM, 18-bits data bus and 72Mbit for each

- 256MB FLASH

Communication

Communication Ports

- Four SFP+ connectors

- PCI Express (PCIe) x8 edge connector (includes Windows PCIe drivers)

- One RS422 expansion header

Others

General user input / output:

- 4 LEDs

- 1 LED Array

- 4 push-buttons

- 4 slide switches

- 2 seven-segment displays

- SMA clock input / output

On-Board Clock

- 50MHz Oscillator

- Programmable oscillators Si570, CDCM61001 and CDCM61004

System Monitor and Control

- Temperature sensor

- Fan control

Power

- PCI Express 6-pin power connector, 12V DC Input

- PCI Express edge connector power

Mechanical Specification

- PCI Express standard height and 3/4-length

Block Diagram