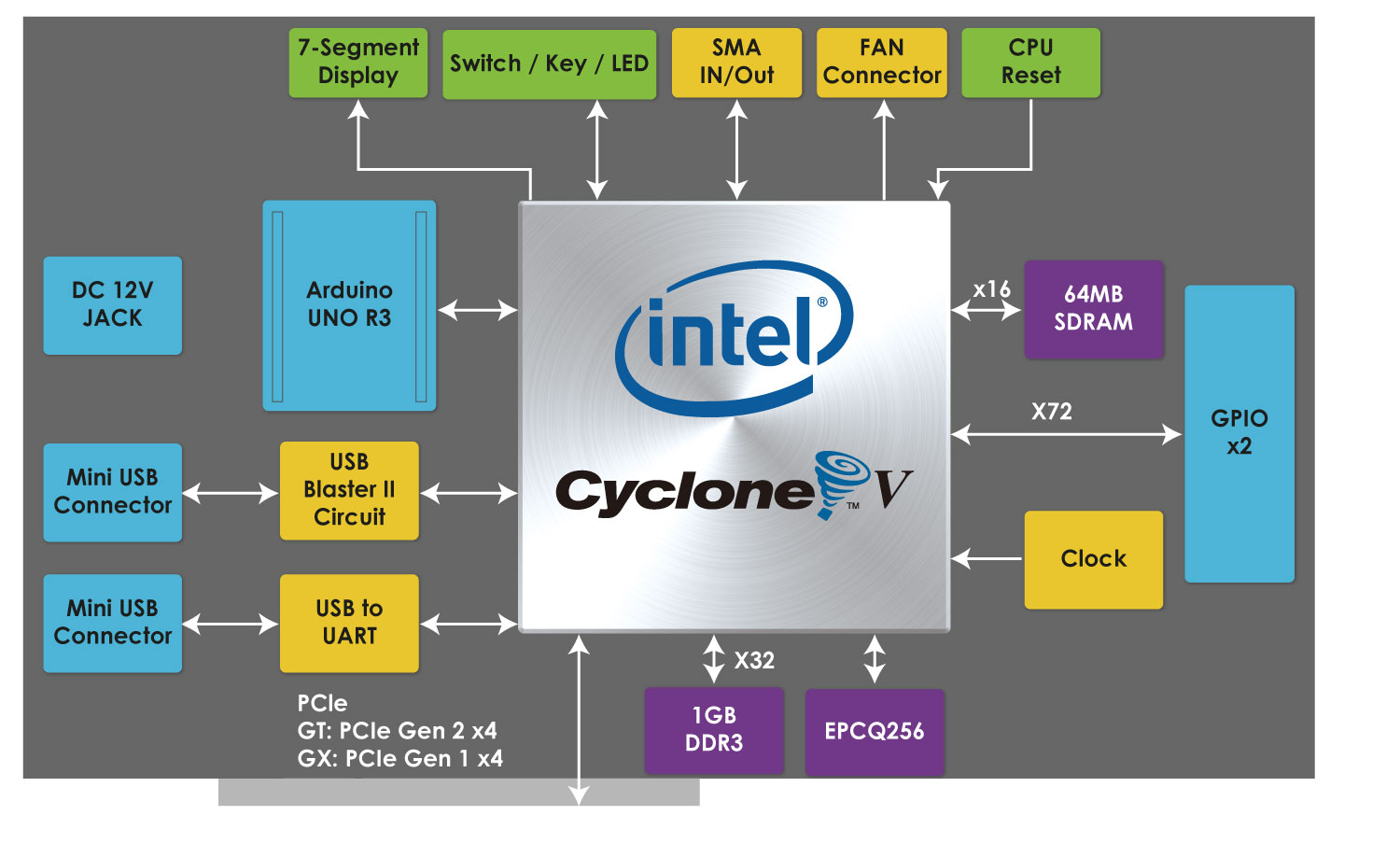

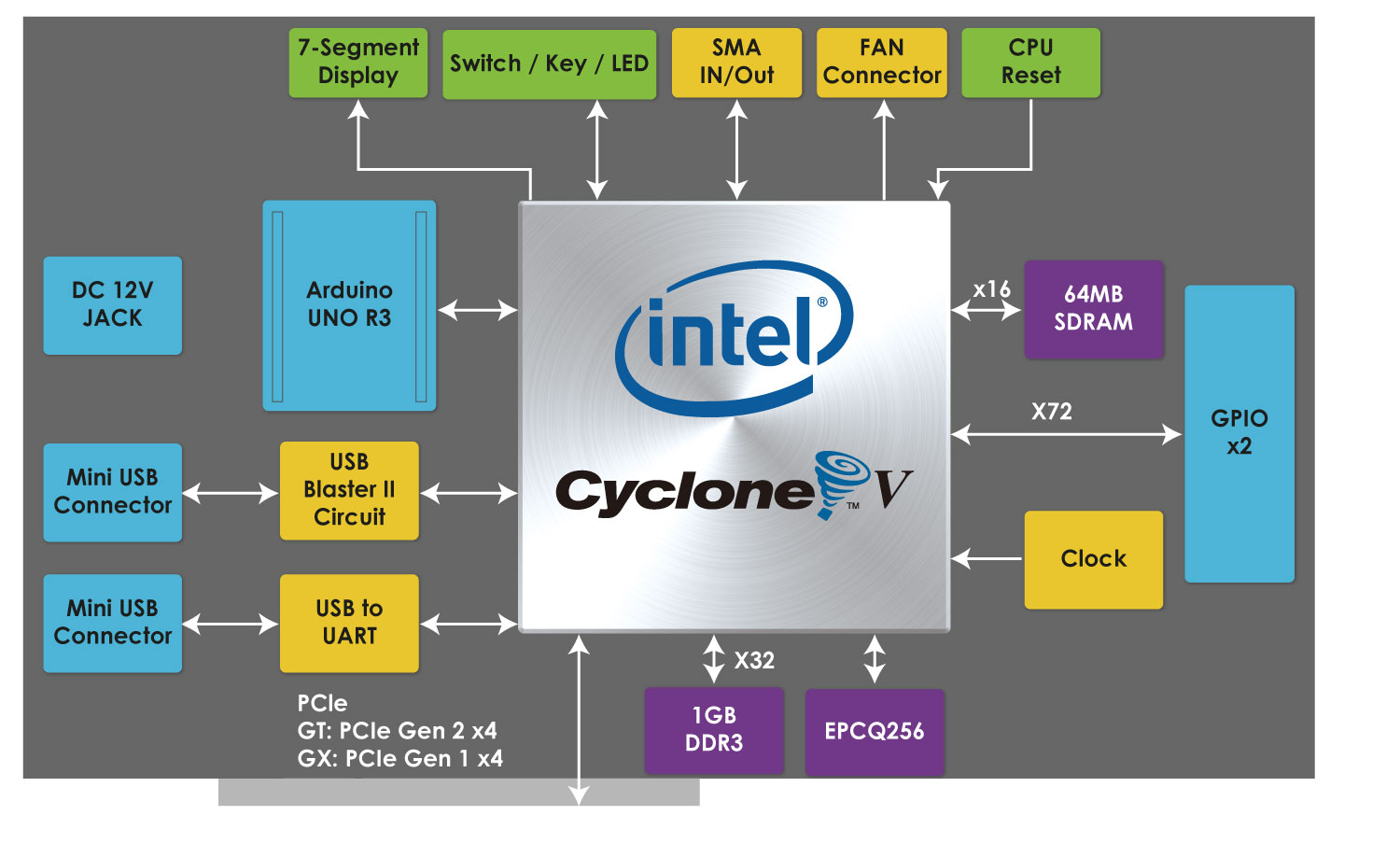

Starter Platform for OpenVINO™ Toolkit

FPGA Device

- Cyclone V

- 301K Programmable Logic Elements

- 13,917 Kbits embedded memory

- Eight Fractional PLLs

- Two Hard Memory Controllers

- Nine Transceivers (the GT speed is 6.144G, and GX speed is 3.125G )

Configuration and Debug

- Quad Serial Configuration device-EPCQ256

- On-Board USB Blaster II (Mini-B USB connector)

Memory Device

- 64MB (32M x16) SDRAM

- 1GB (2 x256M x16) DDR3 SDRAM

Communication

- UART to USB(Mini-B USB connector)

- GT device supports PCIe Gen2x 4(GX device supports PCIe Gen1x 4)

Expansion I/O

- 2 x40 GPIO Header

- 36 General GPIO Pins

- Support 8 pairs LVDS TX and 8 pairs LVDS RX

- Diode protection circuit

- Configurable I/O standards: 1.5/1.8/2.5/3.3V

- One Arduino Uno Revision 3 Expansion Hearder

- Analog ADC

- SPI Interface

- 500Ksps Sampling Rate

- Eight Channels

- Analog Input Range:0 ~ 4.096 V

- Resolution: 12-bit

- Digital IO

- SMA IN/OUT 3.3V single port

Switches, Buttons, LED, and 7-Segments

- 5 User Buttons (4 normal buttons, one CPU_RESET_n)

- 4 User Switches

- 4 LEDs

- 2 7-Segments

Power

- 12V DC input

- PCIe 12V Input

Cooling

Block Diagram