Download

Documents

| Title | Version | Size | Date | Download |

|---|---|---|---|---|

| DE3 User Manual | 1.4 | 9,508(KB) | 2012-05-10 |

CD-ROM

| Title | Version | Size | Date | Download |

|---|---|---|---|---|

| DE3 Control Panel (Support Quartus II 15.0) | 1.1.1 | 2016-09-29 | ||

| DE3 CD-ROM | 2.5.2 | 2015-04-28 | ||

| DE3 System Builder | 1.5.3 | 2013-06-18 | ||

| DE3_HSTC tool (Support Quartus II 11.1) | 1.0.8 | 2012-01-03 | ||

| DE3 Control Panel (Support Quartus II 11.1) | 1.0.6 | 2012-01-03 | ||

| DE3 Demonstrations for QuartusII 10.0 | 2010-08-24 |

Please note that all the source codes are provided "as-is". For further support or modification, please contact Terasic Support and your request will be transferred to Terasic Design Service.

More resources about IP and Dev. Kit are available on Intel User Forums.

Reference Design

- DE3 Control Panel

- USB device/host control demonstration

- SD Card access demonstration

- DDR2 SDRAM demonstration

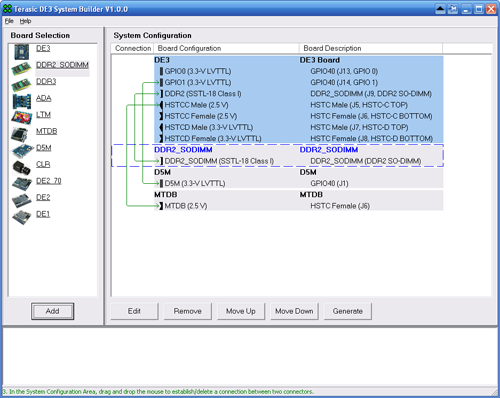

System Builder

DE3 System Builder, a powerful tool comes with the DE3 board. This tool can help users to create the Quartus II project files for DE3 board basic on their custom design. The top-level design file, pin assignment, and I/O standard setting for the DE3 board will be generated automatically by the DE3 System Builder.

The generated Quartus II project files include:

- Quartus II Project File(.qpf)

- Quartus II Setting File(.qsf)

- Top-Level Deign File (.v)

- Synopsis Design Constraints file (.sdc)

- Encrypted Power Configuration Controller (.v)

- Pin Assignment Document (.htm)

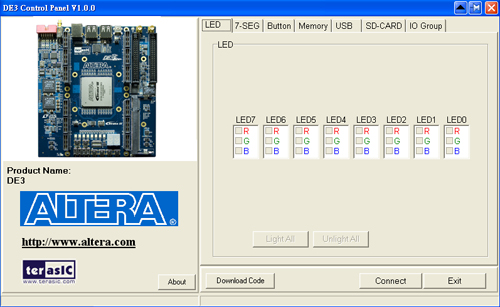

Control Panel

The DE3 board comes with a PC-based Control Panel that allows users to access various components on board. The host computer communicates with the board via USB port. The tool can be used to verify the functionality of components.

Customer Success with Terasic FPGA Platform

|

|