Receive

- Supports up to 2 direct conversion RF receive channels

- Fully integrated snythesizers (including loop filter)

- Data path consists of LNA, Demodulator, LPF, ADC and digital filters

- AGC, Quadrature calibration and DC offset calibration

- NF: 2.5dB @1GHz

- ADC: Continous time sigma-delta, 640MSPS

- Digital Filters: 128 complex taps, decimation between 2 and 48

- Gain: 1dB step size, 80dB analog range, 30dB digital range (post ADC scaling)

- On-chip sensor for temperature-corrected RSSI

Transmit

- Supports up to 2 direct conversion RF transmit channels

- Fully integrated snythesizers (including loop filter)

- Data path consists of digital filters, DAC and Modulators

- Digital Filters: 128 complex taps, interpolation between 2 and 48

- Gain: 0.25dB step size, 86dB range.

- DAC: 320MSPS

Clocking

The clocks are managed by the device and are software programmable. Please refer to the device data sheet for the various clocks within the device. The board provides a 40MHz crystal for the AD9361.

SPI

The SPI signals are directly passed to the HSMC connector.

Control/Monitor

The device allows real-time control via dedicated pins. These signals are passed to the HSMC connector. The functionality of these pins are programmable and includes gain, synchronization, state machine control etc. Please refer to the data sheet for more details.

The device also allows real-time monitoring of internal signals via another set of dedicated pins. Again, these signals are passed to the HSMC connector. The internal signals are multiplexed into these pins- and details of which are best described in the data sheet.

Power

Key components:

| ADP1755 | Low dropout, linear regulator, 1.2A, 1.6 to 3.6V |

| ADP2164ACPZ | High Efficiency,Step-Down DC-to-DC Regulator |

The board receives all the power from the FPGA board through HSMC.

Connectivity

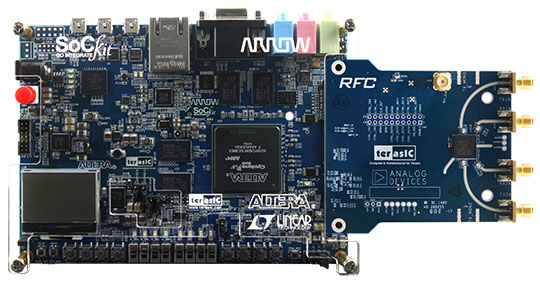

The ARRadio can be connected to the following Terasic FPGA Development Boards:

![]() Connect SoCKit

Connect SoCKit